ARCHITECTURES FOR TRANSACTIONAL MEMORY

A DISSERTATION SUBMITTED TO THE DEPARTMENT OF COMPUTER SCIENCE AND THE COMMITTEE ON GRADUATE STUDIES OF STANFORD UNIVERSITY IN PARTIAL FULFILLMENT OF THE REQUIREMENTS FOR THE DEGREE OF DOCTOR OF PHILOSOPHY

> Austen McDonald June 2009

© Copyright by Austen McDonald 2009 All Rights Reserved I certify that I have read this dissertation and that, in my opinion, it is fully adequate in scope and quality as a dissertation for the degree of Doctor of Philosophy.

(Christos Kozyrakis) Principal Adviser

I certify that I have read this dissertation and that, in my opinion, it is fully adequate in scope and quality as a dissertation for the degree of Doctor of Philosophy.

(Oyekunle Olukotun)

I certify that I have read this dissertation and that, in my opinion, it is fully adequate in scope and quality as a dissertation for the degree of Doctor of Philosophy.

(Mendel Rosenblum)

Approved for the University Committee on Graduate Studies.

### Abstract

Engineers have successfully worked for decades to improve single thread CPU performance, but we have now reached a peak in what a single thread can do. Average programmers are now facing the eventuality that their code must be parallel to take advantage of the performance potential of multi-core chips.

Unfortunately, writing parallel programs is hard because synchronizing accesses to shared state is complex and error-prone—many techniques have been tried, but achieving performance and correctness simultaneously still requires expert programmers, and the method of choice is decades old (locks). Transactional Memory (TM) is a relatively new programming paradigm promising an easier road to correctness and performance using atomic code regions. These regions may then be speculatively executed in parallel, potentially providing performance gains.

This dissertation focuses on architecting and evaluating hardware TM systems. We begin by briefly arguing that TM should be implemented in hardware, since proposed software solutions suffer from poor performance. We then study qualitatively and quantitatively the large design space for hardware TM as defined by primary options such as version management and conflict detection, and vary the secondary options such as the structure of the memory hierarchy, the instructions per cycle, and the configuration of the interconnect. Orthogonally, we determine the semantics and interfaces needed by any hardware TM system to support rich software functionality in modern operating systems and programming languages. Finally, we extend hardware support for transactional execution to create a multi-core architecture that provides cache coherence and memory consistency at the granularity of atomic transactions. We conclude that programs written with transactional memory can achieve comparable to and often superior performance than the same programs written with traditional synchronization methods. Furthermore, a transactional architecture implementing lazy versioning and optimistic conflict detection is the preferred method of implementing TM in hardware due to its simplicity and good performance across a wide range of contention scenarios. Also, to support rich semantics, you need four mechanisms: two-phase transaction commit, software handlers, nested transactions, and nontransactional loads and stores. Finally, a continuously transactional architecture called Transactional Coherence and Consistency (TCC) maintains performance benefits while simplifying the hardware implementation of TM.

# Acknowledgments

Special thanks to my advisor Christos, for picking me as his student and for guiding me through the long Ph.D. process, for teaching me how to do research, and for always reminding me of what's important "at the end of the day."

To Kunle, a.k.a., Papa K., a.k.a., the Wild Nigerian, thanks for keeping me on task and for being there to joke around with.

Also, a thank you goes out to Mendel Rosenblum, my third dissertation reader.

No acknowledgments page would be complete without thanking our hard-working administrators, Teresa Lynn and Darlene Hadding. And of course, thank you to Uncle Sam, the sources of the money they so skillfully administered: NSF Career Award 0546060, NSF Grants CNS-0720905 and CCF-0444470, FCRP contract 2003-CT-888, DARPA NBCH-104009, Army High Performance Computing Research Center HPTi W911NF-07-2-0027-1.

The work for this thesis was not completely my own, but is the product of numerous students' sweat and tears: to Brian David David Carlstrom, thanks for writing "The Robot," for managing the benchmarks, for the Java results, for numerous late-night debugging sessions, and for all the money you loaned me to go to the Thai Cafe; to JaeWoong Chung, even though you never learned to heed the coding standards, your numerous contributions to the simulator code were invaluable; to Hassan Chafi, for help debugging and for the color you added to our group; to Chi Cao Minh, thanks for parallelizing a bunch of benchmarks and for creating STAMP; to Nathan Bronson, thanks for the EP simulator and for introducing me to climbing; to Ben Hertzberg, your x86 simulation code was greatly appreciated; and to Lance Hammond, for inspiring the simulator code and leaving me with the solemn duty of resident graph designer.

Thanks to my advisor at the Georgia Institute of Technology, Kenneth Mackenzie, and to his students, for teaching me what research is, for helping me get to Stanford, and for convincing me I should stay out of a hardware-based Ph.D.

There are too many friends to name, but thank you to all those who celebrated victories with me, persevered through my hard times, offered their shoulders to cry on, and gave me a life outside of the Gates Building.

Of course, I wouldn't be here without my loving. Thanks for threatening to come out here if I didn't finish and thanks especially for all your support throughout my entire life!

Finally, thanks be to God, to whom often I prayed the prayer of Moses: *May the favor of the Lord our God rest upon us; establish the work of our hands for us—yes, establish the work of our hands.* Psalm 90:17.

# Contents

| Al | Abstract |                                            |     |  |  |

|----|----------|--------------------------------------------|-----|--|--|

| A  | cknow    | wledgments                                 | vii |  |  |

| 1  | Intr     | oduction                                   | 1   |  |  |

|    | 1.1      | Transactional Memory                       | 1   |  |  |

|    | 1.2      | The Case for Hardware Transactional Memory | 4   |  |  |

|    | 1.3      | Thesis                                     | 5   |  |  |

|    | 1.4      | Organization                               | 6   |  |  |

| 2  | The      | Architectures of HTM                       | 7   |  |  |

|    | 2.1      | Basic TM Framework                         | 8   |  |  |

|    |          | 2.1.1 Architectural Interface              | 9   |  |  |

|    |          | 2.1.2 Strong versus Weak Isolation         | 10  |  |  |

|    | 2.2      | Eager-Pessimistic (EP)                     | 11  |  |  |

|    | 2.3      | Lazy-Optimistic (LO)                       | 14  |  |  |

|    | 2.4      | Lazy-Pessimistic (LP)                      | 16  |  |  |

|    | 2.5      | Eager-Optimistic (EO)                      | 17  |  |  |

|    | 2.6      | Contention Management                      | 17  |  |  |

|    |          | 2.6.1 Contention Management Policies       | 18  |  |  |

|    |          | 2.6.2 Pathologies                          | 19  |  |  |

|    |          | 2.6.3 Universal Contention Manager         | 21  |  |  |

|    | 2.7      | Virtualization                             | 23  |  |  |

|    | 2.8      | Other Uses of HTM                          | 25  |  |  |

|   | 2.9  | Related Work                                            | 26 |  |  |

|---|------|---------------------------------------------------------|----|--|--|

| 3 | Eval | luation of HTM Design Space 29                          |    |  |  |

|   | 3.1  | Expected Performance                                    | 29 |  |  |

|   | 3.2  | Experimental Setup                                      | 32 |  |  |

|   |      | 3.2.1 Eager-Pessimistic                                 | 33 |  |  |

|   |      | 3.2.2 Lazy-Optimistic                                   | 36 |  |  |

|   |      | 3.2.3 Lazy-Pessimistic                                  | 37 |  |  |

|   |      | 3.2.4 Contention Management                             | 37 |  |  |

|   | 3.3  | Benchmarks for Evaluation                               | 39 |  |  |

|   |      | 3.3.1 bayes                                             | 39 |  |  |

|   |      | 3.3.2 genome                                            | 40 |  |  |

|   |      | 3.3.3 intruder                                          | 42 |  |  |

|   |      | 3.3.4 kmeans                                            | 42 |  |  |

|   |      | 3.3.5 labyrinth                                         | 42 |  |  |

|   |      | 3.3.6 ssca2                                             | 43 |  |  |

|   |      | 3.3.7 vacation                                          | 43 |  |  |

|   |      | 3.3.8 yada                                              | 44 |  |  |

|   |      | 3.3.9 barnes                                            | 44 |  |  |

|   |      | 3.3.10 mp3d                                             | 45 |  |  |

|   |      | 3.3.11 radix                                            | 45 |  |  |

|   |      | 3.3.12 swim                                             | 45 |  |  |

|   | 3.4  | Baseline Evaluation                                     | 46 |  |  |

|   | 3.5  | Contention Management in Pessimistic Conflict Detection | 48 |  |  |

|   |      | 3.5.1 Discussion                                        | 51 |  |  |

|   | 3.6  | Comparing Transactional Systems                         | 52 |  |  |

|   | 3.7  | Comparing to Traditional Parallelization                | 58 |  |  |

|   | 3.8  | Shallow vs. Deep Memory Hierarchy                       | 60 |  |  |

|   | 3.9  | Instruction-Level Parallelism                           | 63 |  |  |

|   | 3.10 | Interconnect Parameters                                 | 66 |  |  |

|   | 3.11 | Related Work                                            | 69 |  |  |

|   | 3.12                                  | Concl    | lusions                                         | 72  |  |  |  |

|---|---------------------------------------|----------|-------------------------------------------------|-----|--|--|--|

| 4 | The Architectural Semantics of HTM 75 |          |                                                 |     |  |  |  |

|   | 4.1                                   | The N    | leed for Rich HTM Semantics                     | 77  |  |  |  |

|   | 4.2                                   | HTM      | Instruction Set Architecture                    | 79  |  |  |  |

|   |                                       | 4.2.1    | Two-phase Commit                                | 82  |  |  |  |

|   |                                       | 4.2.2    | Commit Handlers                                 | 82  |  |  |  |

|   |                                       | 4.2.3    | Violation Handlers                              | 83  |  |  |  |

|   |                                       | 4.2.4    | Abort Handlers                                  | 84  |  |  |  |

|   |                                       | 4.2.5    | Nested Transactions                             | 84  |  |  |  |

|   |                                       | 4.2.6    | Nested Transactions and Handlers                | 86  |  |  |  |

|   |                                       | 4.2.7    | Non-Transactional Loads and Stores              | 88  |  |  |  |

|   |                                       | 4.2.8    | Discussion                                      | 89  |  |  |  |

|   | 4.3                                   | Flexib   | oly Building Languages and Systems              | 90  |  |  |  |

|   | 4.4                                   | Hardv    | ware Implementation                             | 93  |  |  |  |

|   |                                       | 4.4.1    | Two-Phase Commit                                | 93  |  |  |  |

|   |                                       | 4.4.2    | Commit, Violation, and Abort Handlers           | 94  |  |  |  |

|   |                                       | 4.4.3    | Nested Transactions                             | 95  |  |  |  |

|   | 4.5                                   | Evalu    | ation                                           | 99  |  |  |  |

|   |                                       | 4.5.1    | Performance Optimizations with Nesting          | 99  |  |  |  |

|   |                                       | 4.5.2    | I/O within Transactions                         | 101 |  |  |  |

|   |                                       | 4.5.3    | Conditional Synchronization within Transactions | 102 |  |  |  |

|   | 4.6                                   | Concl    | lusion                                          | 103 |  |  |  |

| _ | A 11 7                                | <b>F</b> |                                                 | 105 |  |  |  |

| 5 |                                       |          | ctions All the Time                             | 105 |  |  |  |

|   | 5.1                                   |          | nuous Transactional Execution                   | 107 |  |  |  |

|   | 5.2                                   |          | actional Coherence and Consistency              | 109 |  |  |  |

|   | 5.3                                   | Ŭ        | n Alternatives                                  | 111 |  |  |  |

|   |                                       | 5.3.1    | Coherence Granularity                           | 111 |  |  |  |

|   |                                       | 5.3.2    | Coherence Protocol                              | 112 |  |  |  |

|   | _                                     | 5.3.3    | Commit Protocol                                 | 113 |  |  |  |

|   | 5.4                                   | Perfor   | rmance Evaluation                               | 114 |  |  |  |

| Bi | bliog | liography 133 |                                                     |     |  |  |

|----|-------|---------------|-----------------------------------------------------|-----|--|--|

| 6  | Con   | clusio        | ns and Future Work                                  | 131 |  |  |

|    | 5.5   | Concl         | usions                                              | 128 |  |  |

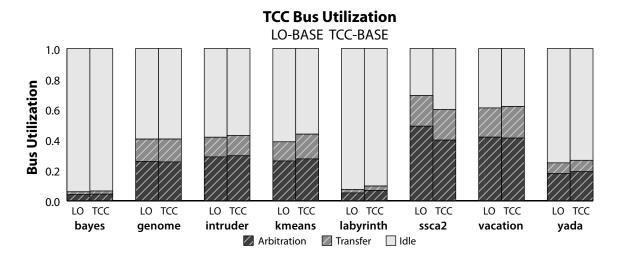

|    |       | 5.4.6         | Bus Utilization                                     | 127 |  |  |

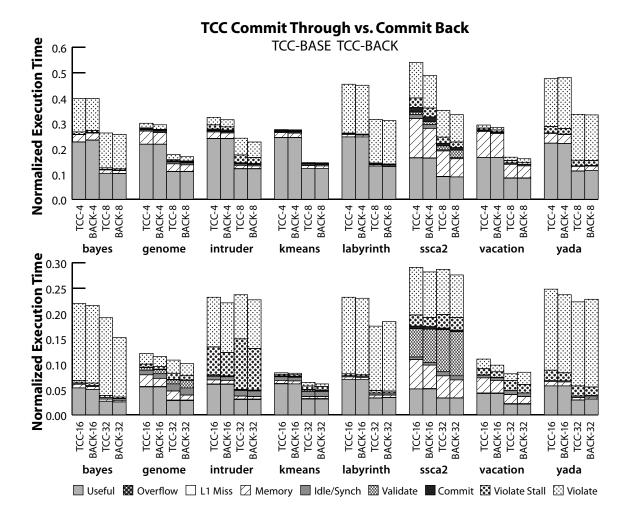

|    |       | 5.4.5         | Commit Protocol: Commit-through versus Commit-back  | 124 |  |  |

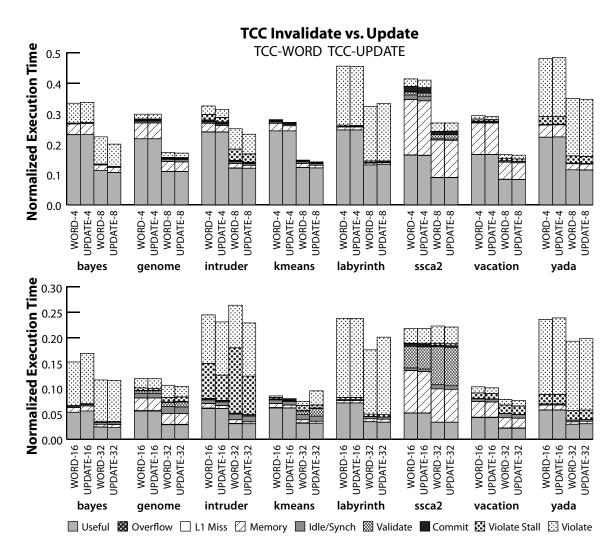

|    |       | 5.4.4         | Coherence Protocol: Update versus Invalidate        | 121 |  |  |

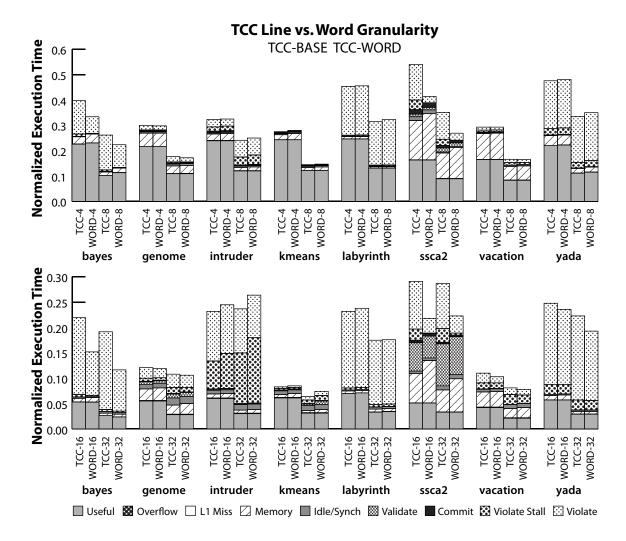

|    |       | 5.4.3         | Coherence Granularity: Line-level versus Word-level | 119 |  |  |

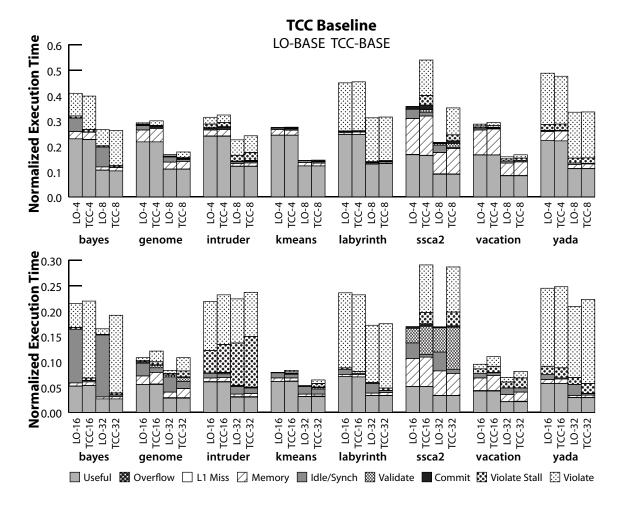

|    |       | 5.4.2         | Baseline Evaluation                                 | 115 |  |  |

|    |       | 5.4.1         | Methodology                                         | 114 |  |  |

# List of Tables

| 2.1 | The fundamental design space of transactional memory                     |     |  |

|-----|--------------------------------------------------------------------------|-----|--|

| 2.2 | Qualitative performance evaluations in the fundamental TM design space.  | 12  |  |

| 3.1 | Default simulator parameters. Experiments use this setup unless other-   |     |  |

|     | wise noted                                                               | 33  |  |

| 3.2 | Cache and transactional statistics for benchmark applications            | 41  |  |

| 3.3 | Descriptions of each of the components of execution time                 | 46  |  |

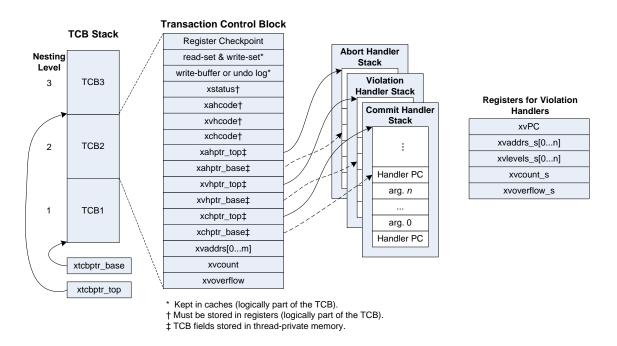

| 4.1 | State needed for rich HTM semantics.                                     | 80  |  |

| 4.2 | Instructions needed for rich HTM semantics.                              | 81  |  |

| 4.3 | HTM mechanisms needed to implement various TM programming lan-           |     |  |

|     | guages                                                                   | 90  |  |

| 5.1 | Cache and transactional statistics for benchmark applications under con- |     |  |

|     | tinuous transactions                                                     | 115 |  |

| 5.2 | Speedups on each of the TCC systems.                                     | 130 |  |

# **List of Figures**

| 2.1  | Basic multicore TM environment.                                                | 8  |

|------|--------------------------------------------------------------------------------|----|

| 2.2  | How optimistic and pessimistic conflict detection schemes work                 | 13 |

| 2.3  | Contention management pathologies                                              | 20 |

| 3.1  | Undo log unrolling implementation                                              | 35 |

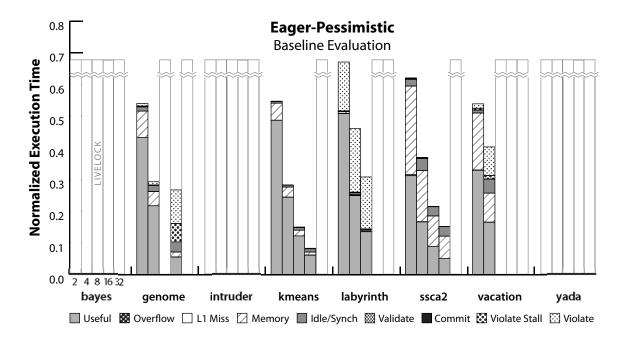

| 3.2  | Execution time breakdown of STAMP on EP-BASE                                   | 47 |

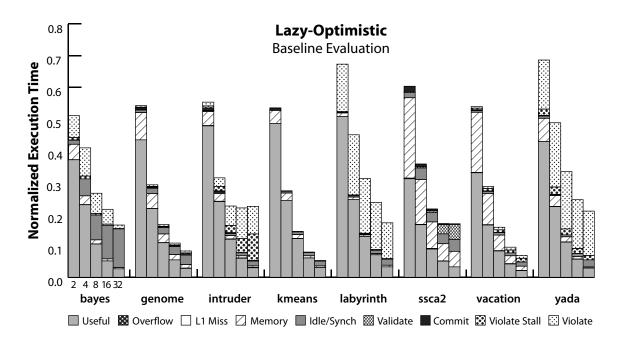

| 3.3  | Execution time breakdown of STAMP on LO-BASE.                                  | 47 |

| 3.4  | Execution time breakdown of STAMP on LP-BASE.                                  | 48 |

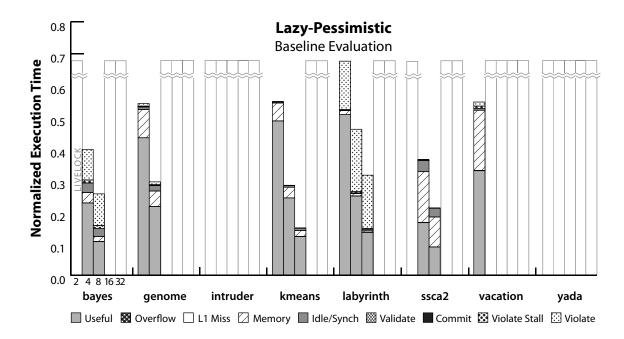

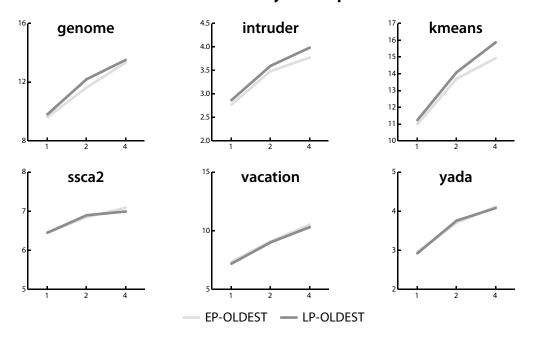

| 3.5  | Comparing speedups of different the contention management configura-           |    |

|      | tions                                                                          | 49 |

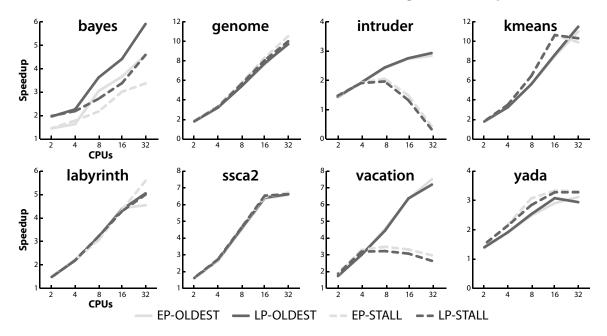

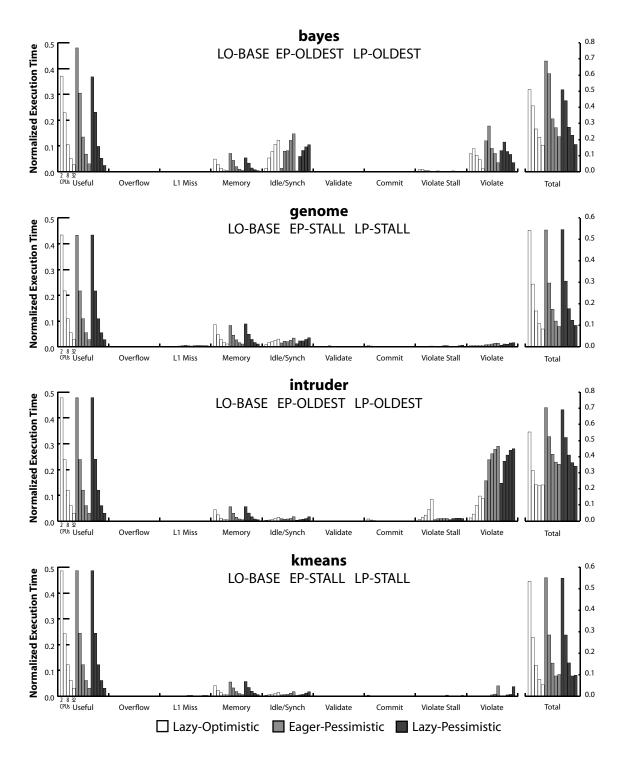

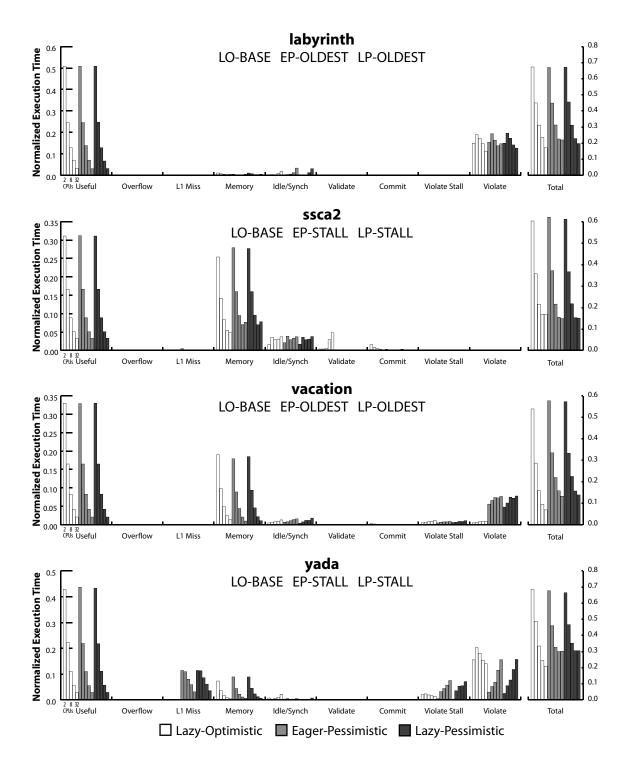

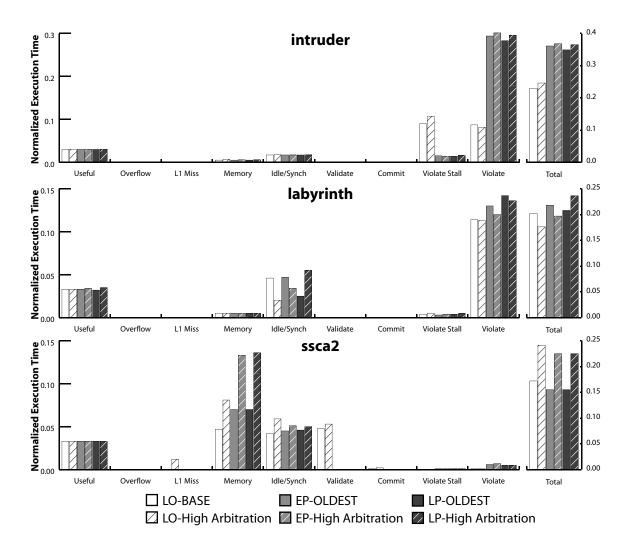

| 3.6  | Execution time breakdown of the best evaluated contention management           |    |

|      | configurations, by application, of the first four STAMP applications across    |    |

|      | all systems                                                                    | 54 |

| 3.7  | Execution time breakdown of the best evaluated contention management           |    |

|      | configuration, by application, of the second four STAMP applications across    |    |

|      | all systems                                                                    | 55 |

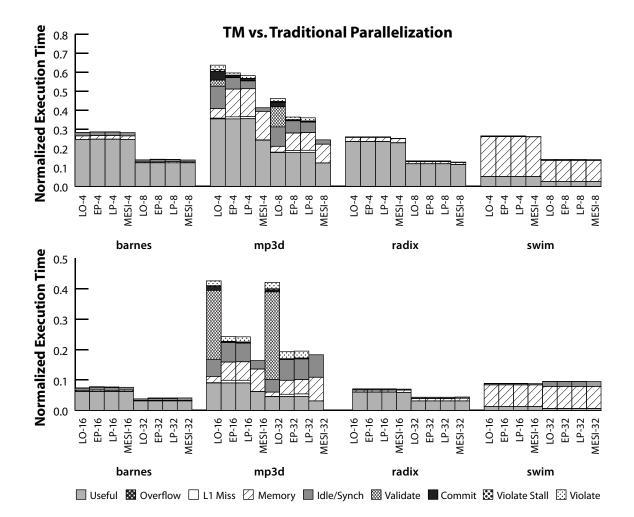

| 3.8  | Execution time breakdown comparison between TM and traditional MESI            |    |

|      | parallelization.                                                               | 59 |

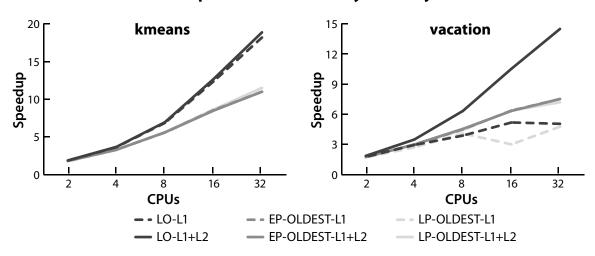

| 3.9  | Speedups of kmeans and vacation on LO, EP, and LP with and without a           |    |

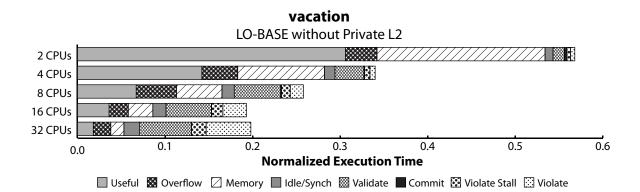

|      | private L2                                                                     | 62 |

| 3.10 | Execution time breakdown of vacation on LO with only a private L1              | 62 |

| 3.11 | Speedups of all three systems on a single issue, a 2-issue, and a 4-issue CPU. | 63 |

| 3.12 | Execution time breakdown, on all three systems, of selected STAMP appli-       |    |

|      | cations using a higher arbitration time.                                       | 67 |

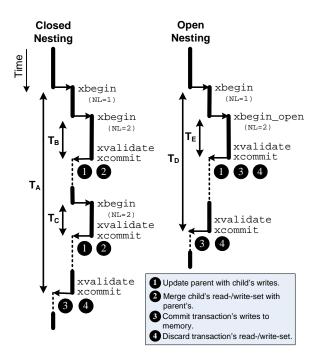

| 4.1 | Timeline of three nested transactions: two closed-nested and one open-      |     |  |

|-----|-----------------------------------------------------------------------------|-----|--|

|     | nested                                                                      | 85  |  |

| 4.2 | The Transaction Stack.                                                      | 87  |  |

| 4.3 | Conditional synchronization using open nesting and violation handlers $\ .$ | 91  |  |

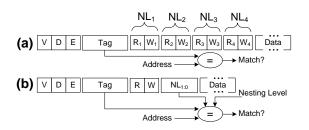

| 4.4 | Cache line structure for denoting nesting levels                            | 96  |  |

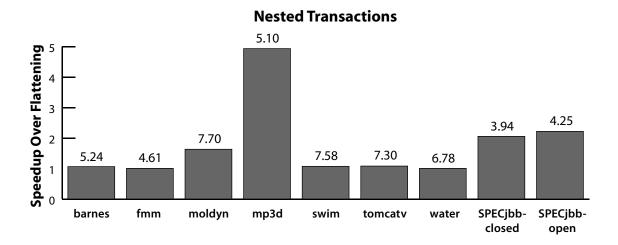

| 4.5 | Performance improvement with full nesting support over flattening           | 100 |  |

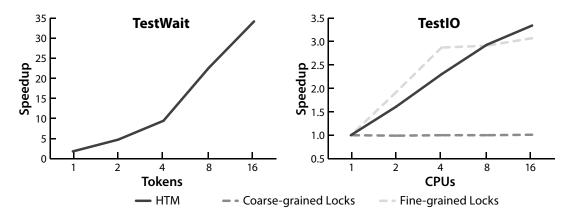

| 4.6 | Performance of transactional conditional synchronization.                   | 103 |  |

|     |                                                                             |     |  |

| 5.1 | Execution time breakdown of STAMP on TCC-BASE.                              | 117 |  |

| 5.2 | Execution time breakdown of STAMP on TCC-WORD.                              | 120 |  |

| 5.3 | Execution time breakdown of STAMP on TCC-UPDATE                             | 122 |  |

| 5.4 | Execution time breakdown of STAMP on TCC-BACK.                              | 125 |  |

| 5.5 | TCC bus utilization on STAMP applications.                                  | 128 |  |

### Chapter 1

# Introduction

Mainstream computing has reached a critical juncture. On one hand, with Instruction-Level Parallelism (ILP) techniques running out of steam, multicore processors are the norm. On the other hand, writing correct and efficient multithreaded programs with conventional programming models is still an incredibly complex task limited to a few expert programmers. Unless we develop programming models and execution environments that make parallel programming the common case, the performance potential of multicore machines will be limited to multiprogramming workloads and a few server applications.

### **1.1 Transactional Memory**

A great deal of the difficulty in creating multithreaded programs comes from the need to manage shared state. When two threads need to communicate or operate on shared data, some mechanism must be employed to ensure correct, serializable execution. Mutual exclusion implemented via locks has been the traditional solution to this problem. Programmers use locks by surrounding accesses to shared state with lock() and unlock() pairs. Once a thread enters the lock region, no other threads are allowed to execute the region's code.

While simple in concept, locks present a number of challenges. First, locks present

programmers with a simplicity versus performance tradeoff. A program using few coarsegrained locks is easy to reason about and programmers have a good chance of generating a correct version of such a program. However, with large lock regions, performance will be poor, as mutual exclusion prevents parallelism. On the other hand, a program with many small locks is likely to perform better, but may be difficult implement correctly.

This difficulty stems from a number of sources. First, fine-grained locks require programmers to associate specific locks with specific data items. Unfortunately, this association is only in the programmer's mind, creating opportunities for careless bugs. Using monitors to incorporate locks into data structures [51] may alleviate this problem. However, monitors do not solve the problem of lock composability: using multiple locks requires strict programmer discipline to avoid deadlock and, in the case of monitors, is difficult to do without access to the locks themselves. For example, the published code for Sun's JDK 1.0.2 implementation of java.lang.String.intern() contains an atomicity bug because locks were not acquired in the correct order [15]. Additionally, pathological interactions, like priority inversion and convoying, can be created between locks and system code like context switches.

Another problem with locks is the poor debugging environment offered by most systems. Many mortal programmers who have written lock-based programs have struggled, at one time or another, with the above-listed problems of deadlock or simply forgetting to lock shared accesses. Unfortunately, finding these bugs is difficult without expensive profiling operations and tools. These tools are usually poor because, as we mentioned earlier, locks and the data they protect is not an easy relationship to establish automatically. Additionally, synchronization-related bugs often fail to reproduce consistently.

There are alternatives to locks like non-blocking synchronization, which avoids the deadlock and priority inversion problems of locks. These methods can offer better performance, but correctness is even harder: new problems are created like livelock and starvation. In fact, perfecting non-blocking algorithms even for simple data structures has been the subject of a number of Ph.D. theses.

To address these challenges with locks, it has been proposed that transactional techniques from the realm of databases [34] be applied to general-purpose programming in the form of "transactional memory" (TM) [57, 48, 90]. In TM, large to medium-sized programmer-defined regions are executed by the runtime system atomically, automatically detecting conflicts. This is achieved by tracking what reads occur inside the transaction (the so-called read-set) and what writes occur (the so-called write-set). At some point before the transaction commits, its read- and write-sets are compared to other transactions to detect and resolve conflicts. In this way, transactions implement the A and I (atomicity and isolation) qualities of database transactions. Database transactions also implement consistency, but this is the responsibility of the TM programmer, who must properly managing his own data-structures, and durability, but TM operates on only memory objects and no persistence is guaranteed.

Transactions present a number of advantages over locks. First, by using one simple language construct, atomic {}, users no longer must manage named locks, allowing the compiler to check for closed regions. Additionally, transactions provide atomicity instead of mutual exclusion, which is usually what programmers want when they use locks. In this way, TM allows two transactions to speculatively execute in parallel, improving performance if they do not conflict. In this way, larger atomic regions can be used, and conflicts are detected only if they exist, instead of prevented via mutual exclusion.

Since atomic guarantees atomicity, it avoids the lock combining problem and because there are no named lock regions, composing atomic is trivial (to the programmer that is, we'll talk more about implementation of nested transactions in Section 4.4.3).

There are also enhanced benefits from TM, like easier debugging and using the TM constructs for other applications. Debugging tools are easier to implement because TM systems track information about program reads/writes and their interactions between threads. This information can then be exposed to the programmer and used to better tune and debug their program [20]. TM also has numerous applications outside of simply protecting shared memory accesses. The ability to roll back an action could be useful in security applications where operations should be tried before they are actually done. Also, a useful debugging technique called deterministic replay can be implemented using the rollback features of TM [68, 101, 28]. TM can be used to efficiently implement memory snapshots [28] which can be used for concurrent garbage collection, among other things.

In conclusion, transactional memory is a promising new parallel programming environment, empowering programmers to better utilize the newly available parallelism provided by multicore processors.

#### **1.2** The Case for Hardware Transactional Memory

The first TM systems were hardware systems with very limited "transactions" [57, 48], but researchers soon extended the ideas from these proposals to what we know today as transactional memory [46, 41]. In fact, the fundamental mechanisms of TM may be implemented completely in hardware (we call these systems HTMs), completely in software (STMs), or in a mixture of the two (hybrid TMs). In this section we argue that HTM, even though requiring a more intensive development effort considering its hardware nature, is the preferred way to provide TM.

STMs do have a number of advantages over hardware systems. The biggest advantage of STMs is that they operate on existing hardware, providing immediate support for transactional memory. Also, as we discuss later (Section 2.7), HTM systems require extra support for transactions of arbitrary size and length, whereas STMs manage this case with ease. Additionally, since STMs can track read- and write-sets at very fine granularities, their conflict detection mechanisms may be less susceptible to false sharing. Another benefit of STMs has been the semantic flexibility: researchers have been able to experiment with various transactional languages and constructs without having to build hardware systems first.

Unfortunately, there are also a number of disadvantages to STMs. Read- and writesets in STMs must be managed by added code, creating a great deal of overhead not present in HTMs. This overhead stands to significantly reduces performance gains from concurrency. Additionally, since this management code must be added to any code running inside a transaction, legacy and library code cannot be used within transactions without recompiling. Finally, if strong isolation is desired (see Section 2.1.2), this management code must be added to non-transactional code as well, further degrading performance. These disadvantages are unlikely to disappear unless programmers use very small, infrequent transactions, which mitigates the programming advantages of TM. Because of these tradeoffs, researchers have proposed hybrid, hardware/software, solutions [14, 59, 31, 85]. While these systems begin to bridge the gap between STM and HTM performance, HTM is still significantly better [13].

STM advocates argue that quickly getting TM into the hands of programmers may help to convert them to TM, following up with hardware at a later date. But, first impressions are important: if a new TM programmer sees poor performance, he may not understand that hardware can make it faster, but may instead abandon TM all together. The remainder of this dissertation explores Hardware Transactional Memory: its implementations, performance, and design alternatives.

#### 1.3 Thesis

This dissertation characterizes transactional architectures and explores the design points and potential alternatives. We compare performance between transactional architectures and traditional parallel architectures, examine the semantics needed to support real-world applications, and evaluate the performance and practical considerations surrounding continuous transactions.

My dissertation provides the following specific contributions:

- Programs written with transactional memory can achieve comparable performance to those written by experts with traditional synchronization methods.

- Furthermore, a transactional architecture called "Lazy-Optimistic" is the preferred method of implementing TM in hardware.

- Performance is not enough though, as TM must also support modern languages and operating systems. To do this, you need four mechanisms: two-phase transaction commit, software handlers, nested transactions, and non-transactional loads and stores.

- Finally, we can extend "Lazy-Optimistic" to use transactions as the only means of coherence and consistency, maintaining the performance benefits of TM while even further simplifying the hardware implementation.

### 1.4 Organization

The remainder of this dissertation is organized as follows.

Chapter 2 explores, in detail, the possible architectures for hardware transactional memory, including the so-called "Lazy-Optimistic" scheme, mentioned in the thesis above.

Chapter 3 evaluates the architectures described in Chapter 2 on a number of axes using transactional applications.

Chapter 4 describes the ISA-level semantics for and their implementation in a fullyfunctional transactional memory system that supports modern programming languages and operating systems.

Chapter 5 introduces the concept and semantics of continuous transactions, or "All Transactions All the Time," in a system called Transactional Coherence and Consistency (TCC). I then discuss the merits of such an approach, and evaluate the performance against non-continuous transactional systems.

Chapter 6 concludes, summarizing the impact of my work on the world of transactional memory and parallel computing.

### **Chapter 2**

# **The Architectures of HTM**

Fundamentally, there are three mechanisms needed to implement an atomic and isolated transactional region: *versioning, conflict detection,* and *contention management*. We will describe them briefly here and explain how to put them together to form complete systems in the following sections.

To make a transactional code region appear atomic, all its modifications must be stored and kept isolated from other transactions until commit time. The system does this by implementing a versioning policy. Two versioning paradigms exist: eager and lazy. An eager versioning system stores newly generated transactional values in place and stores previous memory values on the side, in what is called an undo-log. A lazy versioning system stores new values temporarily in what is called a writebuffer, copying them to memory only on commit. In either system, the cache is used to optimize storage of new versions.

To ensure serializability between transactions, conflicts must be detected and resolved. The system detects conflicts by implementing a conflict detection policy, either optimistic or pessimistic. An optimistic system executes transactions in parallel, checking for conflicts only when a transaction commits. Pessimistic systems check for conflicts at each load and store. Similar to versioning, conflict detection also uses the cache, marking each line as either part of the read-set, part of the write-set, or both. The system resolves conflicts by implementing a contention management policy. Many policies exist, some more appropriate for optimistic conflict detection and some more appropriate

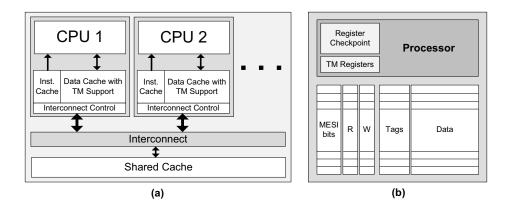

Figure 2.1: Our basic multicore TM environment. Part (a) shows many TM-enabled CPUs on one die, connected with an interconnect. Part (b) shows the details of a transactional CPU, including additions to support TM.

for pessimistic. In this chapter, we describe some popular policies and how they work.

Since each TM system needs both versioning and conflict detection, these options give rise to four distinct TM designs: Eager-Pessimistic (EP), Eager-Optimistic (EO), Lazy-Pessimistic (LP), and Lazy-Optimistic (LO). Table 2.1 briefly describes all four combinations and provides citations to the major proposed implementations of each design.

The remainder of this chapter describes the four basic designs and how to implement them, their advantages and disadvantages, and then discusses potential issues with TM implementations.

### 2.1 Basic TM Framework

For the sake of discussion, we describe TM architectures in the context of a multicore system similar to the one shown in Figure 2.1. Essentially, it is a number of small processor cores, each with some private cache, connected through an interconnect implementing the MESI coherence protocol or some derivative [5, 95]. The TM designs described in this chapter can be used on other architectures like traditional shared memory multiprocessors, distributed shared memory machines [69, 21], and probably others. We do not describe the changes required to implement TM on such systems. To enforce versioning of registers, each core includes a fast, hardware register checkpointing mechanism, shown in Figure 2.1. These units are common in CPUs that support out-of-order execution and checkpoints [67]. Also shown are the additional bits in each cache line used to support conflict detection: a Read (R) bit and a Written (W) bit. Each system uses these to quickly test containment within the read- and write-set, respectively and we assume these can be quickly reset.

Other TM features include status registers (like one to determine whether a transaction is aborting or running) and configuration registers (like the ones required for contention management, see below). Each TM system proposed in literature describes a slightly different set and usage of such registers; a more complete description of the set we use can be found in Chapter 4.

#### 2.1.1 Architectural Interface

All of our designs share a common architectural interface: they all share the same mechanisms to begin and end transactions. For the sake of discussion, let tm\_begin() and tm\_end() represent the code that begins and ends a transaction, respectively. These constructs can be used to build more advanced constructs like atomic [17]. tm\_begin() consists of taking a register checkpoint and changing the status registers to reflect that a transaction has begun. It may also set up any undo log needed in an eager versioning system.

As further described in Chapter 4, tm\_end() has two phases, called validation and commit by the database community [34]. The validation phase ensures that other transactions do not conflict with the completing transaction and commit makes that transaction's write-set available to other transactions. The available mechanisms for validation and commit are dictated by the choice of versioning and conflict detection policy.

Like commit, aborting a transaction depends on how versioning and conflict detection is performed, but there are a few commonalities. We split the abort process into two distinct operations (again, see Chapter 4 for motivation): tm\_discard(), which discards the read- and write-set (R and W bits); and tm\_rollback() which rolls the transaction back to its beginning, including restoring the register checkpoint.

#### 2.1.2 Strong versus Weak Isolation

A key detail for programmers in any TM system is how non-transactional accesses interact with transactions. By definition, transactional accesses are screened from each other using the mechanisms above, but how will a regular, non-transactional load interact with a transaction containing a new value for that address? Or, how will a nontransactional store interact with a transaction that has read that address?

These are issues of the database concept isolation. A TM system is said to implement strong isolation (sometimes called strong atomicity in older literature) when every non-transactional load and store acts like an atomic transaction. Therefore, nontransactional loads cannot see uncommitted data and non-transactional stores cause atomicity violations in any transactions that have read that address. A system where this is not the case is said to implement weak isolation (sometimes called weak atomicity in older literature).

Strong isolation is desired because it is easier to reason about. Additionally, the programmer may have forgotten to surround some shared memory references with transactions, causing bugs. With strong isolation, the programmer will detect this using a simple debug interface because she will see a non-transactional region causing atomicity violations [20]. Also, programs written in one model may work differently on another model [11].

Strong isolation is easy to support in hardware TM: since the coherence protocol already manages load and store communication between processors, transactions can detect non-transactional loads and stores and act appropriately. To implement strong isolation in software TM, non-transactional code must be modified to include read- and write-barriers, potentially crippling performance. Great effort has been expended to remove un-needed barriers, but techniques are complex and performance still significantly worse than HTMs [91, 89].

|                |             | Transactional Memory Des                                                                                          | ign Space                                                                                                                                                        |

|----------------|-------------|-------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                |             | VERSIONING                                                                                                        |                                                                                                                                                                  |

| ION            |             | Lazy                                                                                                              | Eager                                                                                                                                                            |

| LICT DETECTION | Optimistic  | Storing updates in a writebuffer;<br>detecting conflicts at commit<br>time. TCC [39], FlexTM [92],<br>BulkTM [19] | Not practical: waiting to update<br>memory until commit time but<br>detecting conflicts at access time<br>guarantees wasted work and pro-<br>vides no advantage. |

| CONFLICT       | Pessimistic | Storing updates in a writebuffer;<br>detecting conflicts at access time.<br>LTM [8], VTM [80]                     | Updating memory, keeping<br>old values in undo log; de-<br>tecting conflicts at access<br>time. LogTM [69], UTM [8],<br>MetaTM [82]                              |

Table 2.1: The fundamental design space of transactional memory (versioning and conflict detection). Included are references to significant recent proposals for HTMs of each type, if applicable.

### 2.2 Eager-Pessimistic (EP)

The first TM design we describe is Eager-Pessimistic. An EP system stores its write-set "in place" (hence the name "eager") and, to support rollback, stores the old values of overwritten lines in an "undo log". Processors use the W and R cache bits to track readand write-sets and detect conflicts when receiving snooped load requests. Perhaps the most notable examples of EP systems in the literature are LogTM [69] and UTM [8].

Beginning a transaction in an EP system is much like beginning a transaction in other systems: tm\_begin() takes a register checkpoint and initializes any status registers. An EP system also requires initialing the undo log, the details of which are dependent on the log format, but probably involves initializing a log base pointer to a region of preallocated, thread-private memory and clearing a log bounds register. Section 3.2 describes the log format we implemented for our experiments, but many other formats could be used.

**Versioning:** In EP, the MESI state transitions are left mostly unchanged due to the way eager versioning works. Of course, outside a transaction, MESI is completely unchanged. When reading a line inside a transaction, the standard coherence transitions apply  $(S \rightarrow S,$

| Qualitative Comparison                                                                                                                                                                                                                                                                                                                                                                                                                        |                                                                                                                                                                                                                                                                                                                                                                                                                                   |  |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| VERSIONING                                                                                                                                                                                                                                                                                                                                                                                                                                    |                                                                                                                                                                                                                                                                                                                                                                                                                                   |  |

| Lazy<br>+ No additional per store access penalty.<br>- Commit may be slower, requiring per<br>cache line memory transactions, making<br>transactions with high writes to instruc-<br>tions ratios vulnerable to performance<br>degradation.<br>+ Rollback is fast, with only local changes<br>required.                                                                                                                                       | <ul> <li>Eager</li> <li>Per store access penalty: old value must<br/>be written to undo log.</li> <li>+ Commit-in-place makes commit in-<br/>stantaneous.</li> <li>- Undo log must be applied making roll-<br/>back slow.</li> </ul>                                                                                                                                                                                              |  |

| CONFLICT ]                                                                                                                                                                                                                                                                                                                                                                                                                                    | DETECTION                                                                                                                                                                                                                                                                                                                                                                                                                         |  |

| Optimistic                                                                                                                                                                                                                                                                                                                                                                                                                                    | Pessimistic                                                                                                                                                                                                                                                                                                                                                                                                                       |  |

| <ul> <li>+ Because conflicts are detected at commit time, no information need be exchanged on a per access basis.</li> <li>- At validation time however, the writeset must be communicated to all other transactions for conflict checking.</li> <li>- "Doomed" transactions, containing access that will cause conflicts are allowed to continue, wasting resources.</li> <li>+ However, more serializable schedules are allowed.</li> </ul> | <ul> <li>Conflict detection on the critical path:</li> <li>each load must be seen by all transactions to detect conflicts and a contention management decision may potentially be made on each access.</li> <li>+ No additional validation time required since exclusive rights to lines are acquired on access.</li> <li>+ "Doomed" transactions die early.</li> <li>But, not all serializable schedules are allowed.</li> </ul> |  |

Table 2.2: Qualitative performance evaluations in the fundamental TM design space.

$I \rightarrow S$ , or  $I \rightarrow E$ ), issuing a load miss as needed, but the R bit is also set. Likewise, writing a line applies the standard transitions ( $S \rightarrow M$ ,  $E \rightarrow I$ ,  $I \rightarrow M$ ), issuing a miss as needed, but also sets the W bit. The first time a line is written, the old version of the entire line is loaded then written to the undo log to preserve it in case the current transaction aborts. The newly written data is then stored "in-place," over the old data.

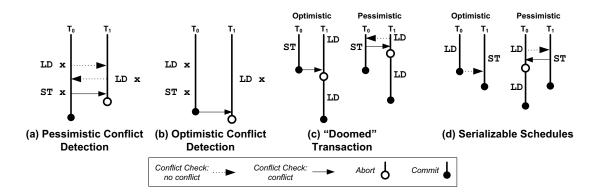

**Conflict Detection:** Pessimistic conflict detection uses coherence messages exchanged on misses or upgrades to look for conflicts between transactions (see Figure 2.2(a)). When a read miss occurs within a transaction, other processors receive a load request. Of course, they ignore the request if they do not have the line. If they have it non-speculatively

Figure 2.2: How optimistic and pessimistic conflict detection schemes work and some tradeoffs in conflict detection. (a) pessimistic conflict detection. (b) optimistic conflict detection. (c) how optimistic conflict detection wastes work by allowing "doomed" transactions to continue, while pessimistic does not. (d) how optimistic allows more serializable schedules to coexist, while pessimistic does not.

or have the line R, they downgrade their line to S and perhaps issue a cache-to-cache transfer if they have the line in MESI's M or E state. But if the cache has the line W, then a conflict is detected between the two transactions and some action must be taken immediately.

Similarly, when a transaction seeks to upgrade a line from shared to modified (on its first write), it issues an exclusive load request, which is also used to detect conflicts. If a receiving cache has the line non-speculatively, they invalidate it and perhaps issue a cache-to-cache transfer (M or E states). But, if the line is R or W, a conflict is detected.

**Validation:** Because conflict detection is performed on every load, a transaction always has exclusive access to its write-set. Therefore, validation does not require any additional work.

**Commit:** Since eager versioning stores the new version of data items in place, the commit process simply clears the W and R bits and discards the undo log (this is very fast).

Abort: When a transaction rolls back, the original version of each cache line in the undo log must be restored, a process called "unrolling" or "applying" the log. This is done during tm\_discard() and must be atomic with regard to other transactions. Specifically, the write-set must still be used to detect conflicts: this transaction has the only correct

version of lines in its undo log and requesting transactions must wait for the correct version to be restored from the log. The log can be applied using a hardware state machine or software abort handler. For our systems, we implemented a software log unroller, described in Section 3.2.

**Advantages:** Commit is simple and since it is in-place, very fast. Similarly, validation is a no-op.

Pessimistic detects conflicts early, as shown in Figure 2.2(c), avoiding "doomed" transactions:  $T_0$  and  $T_1$  are involved in a Write-After-Read dependency which is detected immediately in pessimistic conflict detection, but not until the writer commits in optimistic.

**Disadvantages:** As described above, the first time a cache line is written, the old value must be written to the log, incurring extra cache accesses. Aborts are expensive as they require undoing the log. For each cache line in the log, a load must be issued, perhaps going as far as main memory before continuing to the next line.

Pessimistic conflict detection also prevents certain serializable schedules from existing. Figure 2.2(d) describes this phenomenon:  $T_0$  reads a line and  $T_1$  later writes to the same line. When  $T_1$  attempts to upgrade its line to M, it detects a conflict and aborts  $T_0$ . But, a serializable schedule exists for these transactions (namely  $T_0$ ,  $T_1$ ), and is allowed by optimistic conflict detection.

Additionally, because conflicts are handled as they occur, there is a potential for livelock and careful contention management mechanisms must be employed to guarantee forward progress (see Section 2.6).

### 2.3 Lazy-Optimistic (LO)

Another popular TM design is Lazy-Optimistic (LO), which stores its write-set in a "writebuffer" or "redo log" and detects conflicts at commit time (still using the R and W bits). An LO system exploits different tradeoffs than an EP system, and has been chiefly advocated by the TCC [39] system, further described in Chapter 5.

**Versioning:** Just as in the EP system, the MESI protocol is enforced outside of transactions. Once inside a transaction, reading a line incurs the standard MESI transitions but also sets the R bit. Likewise, writing a line sets its W bit, but handling the MESI transitions is different. First, with lazy versioning, the new versions of written data are stored in the cache hierarchy until commit while other transactions have access to old versions available in memory or other caches (see potential problems with cache overflow in Section 2.7). To make available the old versions, dirty lines must be evicted when first written by a transaction. Second, no upgrade misses are needed because of optimistic conflict detection: if a transaction has a line in the S state, it can simply write to it and upgrade to M without communicating with other transactions because conflict detection is done at commit time.

**Conflict Detection and Validation:** To validate a transaction and detect conflicts, LO communicates the addresses of speculatively modified lines to other transactions only when it is preparing to commit (see Figure 2.2(b)). On validation, the processor sends one, potentially large, network packet containing all the addresses in the write-set. Data is not sent, but left in the committer's cache and marked dirty (M). To build this packet without searching the cache for lines marked W, we use a simple bit vector, called a "store buffer," with one bit per cache line to track these speculatively modified lines.

Other transactions use this address packet to detect conflicts: if an address is found in the cache and the R and/or W bits are set, a conflict is initiated. If the line is found but neither R nor W is set, the line is simply invalidated, like processing an exclusive load.

Of course, to support transaction atomicity, these address packets must be handled atomically, i.e., no two address packets may exist at once with the same addresses. In our LO system, we achieve this by simply acquiring a global commit token before sending the address packet (see Section 3.2). However, a two-phase commit scheme could be employed by first sending out the address packet, collecting responses, enforcing an ordering protocol (perhaps oldest transaction first), and committing once all responses are satisfactory [21].

**Commit:** Once validation has occurred, commit needs no special treatment: simply clear W and R bits and the store buffer. The transaction's writes are already marked dirty in the cache and other caches' copies of these lines have been invalidated via the address packet. Other processors can then access the committed data through the regular coherence protocol.

**Abort:** Rollback is equally easy: because the write-set is contained within the local caches, we simply invalidate these lines then clear W and R bits and the store buffer. The store buffer allows us to easily find W lines to invalidate without the need to search the cache. **Advantages:** Aborts are very fast, requiring no additional loads or stores and making only local changes. More serializable schedules can exist (see Figure 2.2(d) and the discussion for EP), which allows an LO system to more aggressively speculate that transactions are independent, perhaps improving performance. Finally, late detection of conflicts can make guaranteeing forward progress easier (see Section 2.6).

**Disadvantages:** Validation takes global communication time proportional to size of writeset. Doomed transactions can waste work since conflicts are detected only at commit time. See Figure 2.2(c) and the above description for EP.

#### 2.4 Lazy-Pessimistic (LP)

Lazy-Pessimistic (LP) represents a third TM design option, sitting somewhere between EP and LO: storing newly written lines in a writebuffer but detecting conflicts on a peraccess basis. LP has been proposed in the form the LTM [8] and VTM [80] systems.

**Versioning:** Versioning is similar but not identical to that of LO: reading a line sets its R bit, writing a line sets its W bit, and a store buffer is used to track W lines in the cache. Also, dirty lines must be evicted when first written by a transaction, just as in LO. However, since conflict detection is pessimistic, load exclusives must be performed when upgrading a transactional line from I,S $\rightarrow$ M, unlike in LO.

**Conflict Detection:** LP's conflict detection operates the same as EP's: using coherence messages to look for conflicts between transactions.

**Validation:** Like in EP, pessimistic conflict detection ensures that at any point, a running transaction has no conflicts with any other running transaction, so validation is a no-op. **Commit:** Commit needs no special treatment: simply clear W and R bits and the store buffer, like in LO.

**Abort:** Rollback is also like that of LO: simply invalidate the write-set using the store buffer and clear the W and R bits and the store buffer.

**Advantages:** Like LO, aborts are very fast. Like EP, its pessimistic conflict detection avoids doomed transactions (Figure 2.2(c)).

**Disadvantages:** Like EP, some serializable schedules are not allowed (Figure 2.2(d)) and conflict detection must be performed on each cache miss.

### 2.5 Eager-Optimistic (EO)

The final combination of versioning and conflict detection is Eager-Optimistic (EO). Unfortunately, EO is not a logical choice for HTM systems: since new transactional versions are written in-place, other transactions have no choice but to notice conflicts as they occur (i.e., as cache misses occur). But since EO waits until commit time to detect conflicts, those transactions become "zombies," continuing to execute, wasting resources, yet are doomed to abort. We do not implement or evaluate any EO system.

EO has proven to be useful in STMs and is implemented by Bartok-STM [43] and McRT [86]. A lazy versioning STM needs to check its writebuffer on each read to ensure that it is reading the most recent value. Since the writebuffer is not a hardware structure, this is expensive, hence the preference for write-in-place eager versioning. Additionally, since checking for conflicts is also expensive in an STM, optimistic conflict detection offers the advantage of performing this operation in bulk.

#### 2.6 Contention Management

We've learned how a transaction rolls back once the system has decided to abort it but, since a conflict involves two transactions, which one should abort, how should that abort be initiated, and when the aborted transaction should be retried? These are questions of Contention Management (CM), a key component to transactional memory. In this section, we describe how the systems we implemented initiate aborts and the various established methods of managing which transactions should abort in a conflict (called the Contention Management Policy).

#### 2.6.1 Contention Management Policies

A Contention Management (CM) Policy is a mechanism to determine which transaction involved in a conflict should abort and when it should be retried. For example, it is often the case that simply retrying immediately does not lead to the best performance, but employing some backoff mechanism would be better. STMs first grappled with finding the best contention management policies and many of the policies outlined below were originally developed for STMs.

Policies draw on a number of measures to make their decisions, including ages of the transactions, size of read- and write-sets, the number of previous aborts, etc. Combinations are endless, but certain combinations have been used in the literature and we describe a number of them here, roughly in order of increasing complexity.

To establish some nomenclature, first note that in a conflict there are two sides: the attacker and the defender. The attacker is the transaction requesting access to a shared memory location. In pessimistic conflict detection, the attacker is the transaction issuing the load or load exclusive. In optimistic, the attacker is the transaction attempting to validate. The defender is the transaction receiving the attacker's request.

The Aggressive [47] policy immediately and always retries either the attacker or the defender. In LO, Aggressive means that the attacker always wins, and so Aggressive is sometimes called committer wins. It was used for the earliest LO systems [66]. For EP, aggressive can be either defender wins or attacker wins.

Restarting a conflicting transaction that will immediately experience another conflict is bound to waste work—namely interconnect bandwidth refilling cache misses. The Polite [47] policy employs exponential backoff (but linear could also be used) before restarting conflicts. To prevent starvation, it guarantees transaction success after some *n* retries.

Of course, one could just choose to randomly abort the attacker or defender (a policy called Randomized [87]). The inventors combine this with a randomized backoff scheme to avoid unneeded contention.

Perhaps wiser than making random choices is to avoid aborting transactions that have done "a lot of work." One measure of work could be a transactions age. Oldest is a simple timestamp method that aborts the younger transaction in a conflict [79]. BulkTM uses this scheme [19]. SizeMatters [82] is like Oldest but instead of transaction age, the number of read/written words is used as the priority. The inventors revert to Oldest after a fixed number of aborts. Karma [87] is similar, using the size of the write-set as priority. Rollback then proceeds after backing off a fixed amount of time. Aborted transactions keep their priorities after being aborted (hence the name Karma). Polka [88] works like Karma but instead of backing off a predefined amount of time, it backs off exponentially more each time.

Since aborting wastes work, it is logical to argue that stalling an attacker until the defender has finished their transaction would lead to better performance. Unfortunately, such a simple scheme easily leads to deadlock:  $T_0$  reads X,  $T_1$  reads Y,  $T_0$  tries to write Y, stalls on  $T_1$ , while  $T_1$  tries to write X, and stalls on  $T_0$ .

Deadlock avoidance techniques can be used to solve this problem. Greedy [36] uses two rules to avoid deadlock: First, if  $T_1$  has lower priority than  $T_0$ , or if  $T_1$  is waiting for another transaction, then  $T_1$  aborts when conflicting with  $T_0$ . Second, If  $T_1$  has higher priority than  $T_0$  and is not waiting, then  $T_0$  waits until  $T_1$  commits, aborts, or starts waiting (in which case the first rule is applied). Greedy provides some guarantees about time bounds for executing a set of transactions. One EP design (LogTM [69]) used a CM policy similar to Greedy to achieve stalling with conservative deadlock avoidance.

We did not cover every contention management policy devised (for example, Kindergarten and Eruption [88]), but we provided a picture of the CM design space. In Chapter 3 we evaluate a few of these policies.

#### 2.6.2 Pathologies

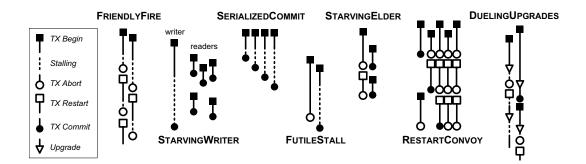

Unfortunately, choosing a CM policy is difficult, not only because there are so many available policies, but also because predicting performance using a particular policy is difficult. Frequently encountered transaction mixes often conspire to create *pathologies*, which are contention phenomena that reduce performance. Some pathologies simply degrade performance while others create worse problems like starvation or livelock. This section describes some of these pathologies (illustrated in Figure 2.3) and what can

Figure 2.3: Illustration of the contention management pathologies. Reproduced from Bobba et al. [12].

be done to alleviate them. Pathologies were first categorized by Bobba et al. [12], and their work contains more details.

The FRIENDLYFIRE pathology may arise when pessimistic conflict detection is combined with an attacker-wins Aggressive CM policy. When one transaction conflicts with and aborts another transaction, then subsequently is aborted by a third transaction. This, of course, can lead to livelock but can be mitigated by using randomized linear backoff before restarting.

STARVINGWRITER may occur in a pessimistic system when one transaction attempts to write and conflicts with a number of concurrent readers. If a CM policy is used that stalls attackers without combining with a priority scheme to ensure forward progress, the writer may stall on the readers, but before the writer can retry its accesses, another reader has appeared. Using a policy like Stall (described in Section 3.2), which combines stalling with transaction age, will guarantee forward progress but performance may still suffer.

FUTILESTALL may also occur in a pessimistic system with a stalling policy when one transaction stalls waiting for another transaction that eventually aborts. In this case, stalling just wasted time. This can be exacerbated in EP because aborting takes extra time to undo the log.

Another pathology that occurs in EP systems with a stalling policy is DUELINGUP-GRADES: when two transactions both read then attempt to write (i.e., upgrade) the same address, conflicts are detected and they attempt to stall on each other, with the deadlock avoidance protocol eventually aborting one. If the continuing thread commits then begins another similar transaction, which frequently occurs in loops, then the restarted transaction may conflict with the new transaction, entering the pathology pattern once again.

Two pathologies may occur in LO systems with an Aggressive, attacker-wins CM policy. Since small transactions reach their commit phase before longer transactions, small transactions can starve older, longer ones, creating the STARVINGELDER pathology. Some priority scheme is required to prevent starvation in these cases. If many similar, conflicting transactions execute concurrently, then the first to commit may abort all others, creating a so-called RESTARTCONVOY. Members of the convoy may repeatedly execute, wasting system resources even though all but one are doomed to abort. A backoff mechanism can help to alleviate RESTARTCONVOY.

SERIALIZEDCOMMIT can occur in optimistic conflict detection systems that serialize at commit time to achieve a global order. Many small transactions may attempt to commit simultaneously, creating contention for global commit permission even though there may be no conflicts. This can be fixed by using a parallel commit scheme like that one described in the LO section above.

In conclusion, it is important to choose a proper contention management policy that avoids pathologies, but this is highly dependent on application characteristics. Pessimistic conflict detection leads to more and more likely pathologies than optimistic, though empirical studies (like those in Chapter 3) are required to determine if pathological transaction mixes really do exist and what their performance impact may be.

# 2.6.3 Universal Contention Manager

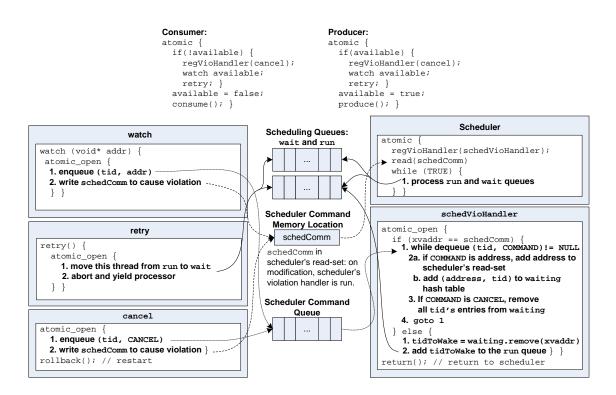

To implement these contention management policies, we introduce a mixed hardware and software solution called the Universal Contention Manager (UCM). The goals of the UCM are to make rapid decisions about which transaction should abort, so as not to degrade performance on each access, but also provide enough flexibility to support many CM policies.

In any policy, the actual abort process begins when one of these transactions executes a software violation handler (see Section 4.2.3 for details). The minimum required handler would call tm\_discard, tm\_rollback, and perhaps undoing the log if the system is EP. This violation handler is the software component of the UCM and is key to supporting a wide range of CM policies without needed to design specific hardware structures to implement each one. Specifically, software handlers have access to any hardware registers tracking transaction state (like length and number of lines read/written) and can store their own software state.

To decide which processor will invoke its software violation handler, the UCM uses two global hardware registers (SENSE and TIEBREAK) and an additional per-processor register (PRIORITY). The PRIORITY register is sent over the interconnect along with each item of coherence traffic (e.g., load miss).

The SENSE register determines which transaction will run its handler: the one with the smaller priority register (SENSE=SMALLERWINS), the one with the larger priority register (SENSE=BIGGERWINS), or to defer to the TIEBREAK setting (SENSE=ALWAYSTIE).

The TIEBREAK register specifies which transaction, the defender or the attacker, should execute their handler in the case of a tie on the priority register or if SENSE is ALWAYSTIE. Possible values for TIEBREAK are DEFENDERWINS (i.e., run the handler on the attacker) or ATTACKERWINS (i.e., run the handler on the defender).

Some examples will help the reader understand the UCM. To implement Aggressive, we do not use the priority register, so we set SENSE to ALWAYSTIE and TIEBREAK to ATTACKERWINS to ensure that the committing transaction is allowed to proceed. The software violation handler then simply executes tm\_discard() and tm\_rollback().

To incorporate the transactions' ages using the UCM (e.g., to implement Oldest), we could set the priority register to the time during tm\_begin(). Oldest would then set SENSE to SMALLERWINS and TIEBREAK to either DEFENDER or ATTACKERWINS. Similarly, to incorporate abort counts or write-set sizes, the software violation handler can store these values in thread-private variables, perhaps copying them into the PRIORITY register for future rapid comparison to the values from other transactions.

Different abort characteristics can also be implemented using the software violation handler. Linear and exponential backoff can be implemented by simply spinning in a loop before calling tm\_discard(); tm\_rollback().

The UCM is very simple hardware yet achieves important goals: making abort conflict resolution decisions quickly and locally while maintaining the flexibility of a software handler.

# 2.7 Virtualization

Because transactions use caches to track read- and write-sets, a number of issues can arise when cache space is exhausted or the cache is needed for another thread, like on a context switch. These are issues of so-called transactional virtualization. This section describes some of the challenges and related work.

First, restricting the user to transactions whose metadata (W and R bits) and data fit in local caches is unacceptable. Studies have found that the common-case behavior of transactional systems is small transactions [27], but also that reasonable programming practices result in transactions too large for some cache structures [8], inducing what is called "cache overflow." Certain architectural extensions can be employed, like victim caches, to significantly reduce the probability that such transactions will exist [66], but no matter how large are local caches, systems will need some method of virtualizing space.

Second, if transactions are employed on a large scale, then it is certain that context switches, page faults, process migration, etc. will occur during a transaction. How can transactional semantics be maintained when cache structures can no longer be used exclusively for one transaction? This problem is called time virtualization. Major challenges include maintaining isolation of yet-to-be-committed data and maintaining conflict detection between running transactions and those "swapped out" of the caches.

There are a number of goals for these virtualization systems. Obviously, they must support transactional semantics like atomicity and isolation, but the presence of virtualizing mechanisms (i.e., hardware and software overhead) should also not affect the common-case transactional performance. Additionally, once a virtualized transaction exists, it is preferable that the performance of other transactions in the system not suffer because of it. Finally, since we assume virtualization will be rarely used, additional complexity (especially hardware complexity) should be avoided. There have been a number of proposals to virtualize transactions, not all achieving every goal or even virtualizing both time and space. What follows is a brief look at some of the proposed mechanisms.

One simple approach to handle space virtualization, chosen by us in early research on LO systems [66], is simply to acquire a global token preventing others from validating, flush out the transaction's write-set (essentially committing), then continue execution, holding the token until encountering a user-defined commit. This approach guarantees atomicity of the overflowed transaction, but punishes the entire system, not just the overflowed transaction. It is also important to note that this approach exposes a transaction's writes to the system before it commits, preventing that transaction from aborting on its own and violating strong isolation (giving non-transaction threads access to uncommitted state). We continue to employ this approach to simplify implementation of our LO system because overflows are rare in our applications.

Ananian et al. [8] were the first to propose an HTM design with more significant solutions to virtualization problems, namely their UTM system, which is EP. UTM is an idealized system utilizing additional per-location memory pointers and global virtual addresses to virtualize both time and space, but at significant overheads. The same work introduces LTM, a more reasonable system, but it lacks time virtualization and limits space virtualization to the size of main memory.

Like LTM, LogTM [69] virtualizes space but not time. One advantage of an eager versioning system like LogTM is that the undo log can grow to arbitrary size without special handling. However, metadata overflow still occurs and LogTM chooses to simply keep the W/R bits on overflowed lines, OR-ing any future metadata modifications. Of course, this causes additional conflicts but it is a simple low-overhead solution. Later LogTM designs used signatures for conflict detection, allowing time virtualization by saving/restoring signatures [105].

VTM [80] is an LP system supporting time and space virtualization. It supports two execution modes, one for common case, non-virtualized transactions, and one for virtualized transactions. Virtualized transactions have their overflowed write-set mapped to virtual memory and similarly, swapped-out transactions also store their state in virtual memory. To accomplish this, VTM uses an additional hardware-managed hash table and a Bloom filter to perform rapid conflict checks.

A number of software-enhanced virtualization mechanisms have also been proposed. HybridTM [31] simply switches to software transactions when virtualization is needed, but requires two copies of all transactional code: one for the HTM and one for the STM. XTM [26] and Page-based TM [23] (PTM) both use extra pages to enable space virtualization. XTM employs lazy versioning, buffering writes in a newly created page, while PTM employs eager versioning, storing its writes in place, keeping the last committed version in a new page. Also, XTM is mostly software while PTM employs more hardware structures. Enhancements to XTM also support line-granularity virtualization.

In conclusion, implementing time and space virtualization is important in any real TM system, but it should be thought of as a rarely-used feature. Virtualization systems need to be tailored to the chosen versioning and conflict detection mechanisms. Eager versioning may make space virtualization easier since you do not have to store new versions separately. Lazy versioning may make virtualizing time easier since you do not have to protect other loads/stores from eagerly-committed data. Despite these biases, efficient solutions exist at all TM design points.

# 2.8 Other Uses of HTM

The hardware TM employs for supporting atomicity and optimistic concurrency can also be used to accelerate a number of important systems applications, not just multithreaded applications. Fundamentally, TM provides isolated memory regions and highlyobservable application behavior, which have wide-ranging applicability in OSs, debugging, optimization, reliability, and security.

Conflict detection requires constant program introspection. This can be used to provide debugging and optimization support. With Transactional Application Profiling Environment (TAPE) [20], we suggested using a conflict logging system to identify potentially fruitful optimizations and to detect non-transactional accesses to shared state. Similarly, having hardware track read- and write-sets enables data race detection [63, 74, 75].

By providing isolation, HTMs already have support for a kind of hardware memory

snapshot, which can greatly improve the ease of developing a host of often serialized application components including concurrent garbage collectors, dynamic profilers, and copy-on-write, as observed by Chung et al. [28].