### MODELS AND METRICS FOR ENERGY-EFFICIENT COMPUTER SYSTEMS

### A DISSERTATION

## SUBMITTED TO THE DEPARTMENT OF ELECTRICAL

#### ENGINEERING

### AND THE COMMITTEE ON GRADUATE STUDIES

### OF STANFORD UNIVERSITY

IN PARTIAL FULFILLMENT OF THE REQUIREMENTS

#### FOR THE DEGREE OF

### DOCTOR OF PHILOSOPHY

Suzanne Marion Rivoire June 2008

© Copyright by Suzanne Marion Rivoire 2008 All Rights Reserved I certify that I have read this dissertation and that, in my opinion, it is fully adequate in scope and quality as a dissertation for the degree of Doctor of Philosophy.

(Christoforos Kozyrakis) Principal Adviser

I certify that I have read this dissertation and that, in my opinion, it is fully adequate in scope and quality as a dissertation for the degree of Doctor of Philosophy.

(Oyekunle Olukotun)

I certify that I have read this dissertation and that, in my opinion, it is fully adequate in scope and quality as a dissertation for the degree of Doctor of Philosophy.

(Parthasarathy Ranganathan)

Approved for the University Committee on Graduate Studies.

## Abstract

Energy efficiency is an important concern in computer systems from small handheld devices to large data centers and supercomputers. Improving energy efficiency requires metrics and models: metrics to assess designs and identify promising energy-efficient technologies, and models to understand the effects of resource utilization decisions on power consumption. To facilitate energy-efficiency improvements, this dissertation presents Joule-Sort, the first completely specified full-system energy-efficiency benchmark; and Mantis, a generic and portable approach to real-time, full-system power modeling.

JouleSort was the first full-system energy-efficiency benchmark with fully specified workload, metric, and rules. This dissertation describes the benchmark design, highlighting the challenges and pitfalls of energy-efficiency benchmarking that distinguish it from benchmarking pure performance. It also describes the design of the machine with the highest known JouleSort score. This machine, consisting of a commodity mobile CPU and 13 laptop drives connected by server-style I/O interfaces, differs greatly from today's commercially available servers.

Mantis generates full-system power models by correlating AC power measurements with software utilization metrics. This dissertation will evaluate several different families of Mantis-generated models on several computer systems with widely varying components and power footprints, identifying models that are both highly accurate and highly portable. This evaluation demonstrates the trade-off between simplicity and accuracy, and it also shows the limitations of previously proposed models based solely on OS-reported component utilization. The simplicity of this black-box approach makes it a useful tool for power-aware scheduling and analysis.

## Acknowledgments

I am grateful to many people for their contributions to this dissertation and to the quality of my life while I worked on it.

First, it has been an honor to work with Christos Kozyrakis, my advisor. I am profoundly grateful to him for his perceptive, patient, and unselfish mentoring over the last six years. He has been an unfailing source of honest and supportive advice in my research and in my career, and because of him, I have become a much more competent and confident scholar and teacher.

I am also deeply thankful to Partha Ranganathan, my mentor at HP Labs. Partha has been amazingly generous in providing me with professional opportunities, starting with the opportunity to work on the research described in this dissertation. He has also been a wise and compassionate mentor whose guidance and support have been indispensable.

I am also grateful to Kunle Olukotun for serving on my reading committee and to Dwight Nishimura for chairing the examining committee for my defense. Kunle's feedback on my work and help during the job search process have been very beneficial to me.

This research would not have been possible without my collaborators and co-authors. Mehul Shah and I worked closely together to bring his idea of an energy-efficiency extension of the Sort Benchmark to fruition. I am grateful to him for his patience and his willingness to help with every aspect of the work. I was also fortunate to work with two dedicated, talented, and highly skilled undergraduate students: Justin Meza, who extended my work in designing energy-efficient sorting systems, and Dimitris Economou, whose work paved the way for the modeling study in this thesis and who contributed to the study of the Itanium machine discussed in Chapter 7. I also greatly appreciate the outside feedback from Luiz Barroso, Wolf-Dietrich Weber, Taliver Heath, Feng Zhao, Kim Shearer, Bill Bolosky, Naga Govindaraju, Chris Reummler, and Jim Gray, and from the participants at UC-Berkeley's RAD Lab retreats.

The work described in Chapter 4 relied on Ordinal Technology's Nsort software, and I am grateful to Ordinal's Chris Nyberg and Charles Koester for their generosity with their time and support. Similarly, the work described in Chapters 6 and 7 relied on software written by Justin Moore and by Stephane Eranian, for whose assistance I am also grateful.

Jacob Leverich provided valuable contributions to several aspects of this research. First, he was indispensable in configuring the hardware and software of the CoolSort machine. Second, he helped to instrument and configure one of the machines used to validate my power models. Third, he was an excellent system administrator for our research group, a job that I am also thankful to him for taking off of my hands. Fourth, hook 'em Horns!

This work also benefited from the administrative and technical assistance of Teresa Lynn, Charlie Orgish, and Joe Little at Stanford; and Annabelle Eseo, Hernan Laffitte, Craig Soules, Malena Mesarina, Christina Solorzano, and Rowena Fernandez at HP. Teresa in particular showed great forbearance during the process of ordering the CoolSort machine piece by piece.

Funding for my doctoral work was provided by several sources. I am grateful to the anonymous donor of my Stanford Graduate Fellowship and to the National Science Foundation for their graduate fellowship. My initial research was done with the support of Cray, and I am grateful to Cray's Steve Scott for his mentoring; he gave me enough independence to build my confidence as a researcher, while always being available for advice and feedback. My subsequent research was supported by HP Labs, for which I am thankful to John Sontag as well as Partha and Mehul; and by Google.

On a more personal level, the support of more senior graduate students has been essential to surviving in Stanford's huge electrical engineering department. From the time I first set foot on the Stanford campus as a prospective graduate student, Kerri Cahoy took me under her wing and introduced me to EE students outside the Computer Systems Lab. Later, when I started doing research, the advice and support of senior students helped me find my way. Bennett Wilburn, Kelly Shaw, John Davis, and Mattan Erez were particularly generous and helpful.

My fellow graduate students at Stanford and in the computer architecture community have made my graduate school years more productive and enjoyable. In particular, Allison Holloway has been there for me from the introductory electrical engineering course in the first semester of our freshman year of college all the way through the Ph.D. process. Additionally, Jayanth Gummaraju, Nju Njoroge, Joel Coburn, Dan Finkelstein, and Nidhi Aggarwal have become good friends and colleagues. Finally, I appreciate the camaraderie and support of my current and former groupmates: Varun Malhotra, Rebecca Schultz (who was also a dedicated research collaborator), Austen McDonald, Chi Cao Minh, Sewook Wee, Woongki Baek, JaeWoong Chung, Michael Dalton, Hari Kannan, and Jacob Leverich.

During graduate school, I have been fortunate to become involved in several IEEE committees. It has been rewarding and inspirational to work with such a diverse and passionate group of engineers, and it has taught me a great deal about my profession. In particular, I have worked on *IEEE Potentials* with Phil Wilsey, Kim Tracy, and George Zobrist since 2002, and they have been generous both in providing professional opportunities and in giving academic and career guidance.

Finally, I am also grateful to all my friends and my entire family for the opportunities and support they provided me. My mother, Elizabeth Rivoire Lee, has been a loving and supportive presence in my life, and learned early not to ask when the Ph.D. would be finished. My late father, Thomas Alexis Rivoire, spent years persuading me that I could and should pursue a technical career, and I know he would be proud of where I am today. I also owe a special debt to the other engineers in the family: my grandfather, Bernard Rider, whose love of math and problem-solving is contagious, and my sister, Kelley Rivoire, who is a great friend with interesting perspectives on our field. The past few years have brought wonderful new additions to my family, including my stepfather, Bob Lee, and my husband, Grant Gavranovic. I am very grateful to Grant for the many years of friendship, love, and support we have shared. He has enriched my life and made every day happier.

## Contents

| Ał | ostrac | t                                              | iv |

|----|--------|------------------------------------------------|----|

| Ac | know   | vledgments                                     | vi |

| 1  | Intr   | oduction                                       | 1  |

|    | 1.1    | Motivation                                     | 2  |

|    | 1.2    | Contributions                                  | 3  |

|    | 1.3    | Dissertation Outline                           | 4  |

| 2  | Ben    | chmarking Energy Efficiency                    | 6  |

|    | 2.1    | Benchmarking Challenges                        | 7  |

|    | 2.2    | Energy-Efficiency Benchmark Goals              | 8  |

|    | 2.3    | Current Energy-Efficiency Metrics              | 10 |

|    |        | 2.3.1 Component-level Benchmarks and Metrics   | 10 |

|    |        | 2.3.2 System-level Benchmarks and Metrics      | 12 |

|    |        | 2.3.3 Data Center-level Benchmarks and Metrics | 14 |

|    |        | 2.3.4 Summary                                  | 15 |

| 3  | The    | Joulesort Benchmark Definition                 | 16 |

|    | 3.1    | Workload                                       | 17 |

|    | 3.2    | Metric                                         | 19 |

|   |      | 3.2.1   | Fixed Energy Budget                       | 19 |

|---|------|---------|-------------------------------------------|----|

|   |      | 3.2.2   | Fixed Time Budget                         | 20 |

|   |      | 3.2.3   | Fixed Input Size                          | 23 |

|   | 3.3  | Bench   | mark Categories                           | 24 |

|   | 3.4  | Measu   | ring Energy                               | 25 |

|   |      | 3.4.1   | System Boundaries                         | 25 |

|   |      | 3.4.2   | Ambient Environment                       | 26 |

|   |      | 3.4.3   | Measurement and Instrumentation           | 26 |

|   | 3.5  | Summa   | ary                                       | 27 |

| 4 | Doci | anina F | nongy Efficient Computer Systems          | 29 |

| 4 |      | 0 0     | nergy-Efficient Computer Systems          |    |

|   | 4.1  |         | Efficiency of Past Sort Benchmark Winners |    |

|   |      | 4.1.1   | Methodology                               | 30 |

|   |      | 4.1.2   | Analysis                                  | 32 |

|   | 4.2  | Evalua  | tion of Commodity Systems                 | 35 |

|   |      | 4.2.1   | Unbalanced Systems                        | 35 |

|   |      | 4.2.2   | Balanced Server                           | 38 |

|   |      | 4.2.3   | Summary                                   | 40 |

|   | 4.3  | Design  | of the JouleSort Winner                   | 40 |

|   |      | 4.3.1   | Details of Winning Configuration          | 41 |

|   |      | 4.3.2   | Varying Hardware Configuration            | 43 |

|   |      | 4.3.3   | Varying Software Configuration            | 51 |

|   |      | 4.3.4   | CPU and I/O Dynamic Power Variation       | 52 |

|   |      | 4.3.5   | Summary                                   | 53 |

|   | 4.4  | Other I | Energy-Efficiency Metrics                 | 53 |

|   | 4.5  | Conclu  | sions                                     | 63 |

| 5 | Pow | r Modeling Background 6                      | 55         |

|---|-----|----------------------------------------------|------------|

|   | 5.1 | Power Modeling Goals                         | 66         |

|   | 5.2 | Power Modeling Approaches                    | 57         |

|   |     | 5.2.1 Simulation-based Power Models          | 58         |

|   |     | 5.2.2 Detailed Analytical Power Models       | 0          |

|   |     | 5.2.3 High-level Black-box Power Models      | 2          |

| 6 | The | Mantis Power Modeling Methodology 7          | 6          |

|   | 6.1 | Overview of Model Development and Evaluation | '7         |

|   | 6.2 | Calibration Process                          | '9         |

|   |     | 6.2.1 Calibration Software Suite             | 80         |

|   |     | 6.2.2 Portability and Limitations            | 81         |

|   | 6.3 | Model Inputs                                 | 32         |

|   | 6.4 | Models Studied                               | 34         |

|   | 6.5 | Evaluation Process                           | 85         |

|   |     | 6.5.1 Introduction                           | 85         |

|   |     | 6.5.2 Machines                               | 86         |

|   |     | 6.5.3 Benchmarks                             | <u>8</u> 9 |

| 7 | Pow | r Modeling Evaluation 9                      | 2          |

|   | 7.1 | Overall Results                              | 13         |

|   | 7.2 | Xeon Server Power Models                     | 12         |

|   | 7.3 | Itanium Server Power Models                  | 18         |

|   | 7.4 | CoolSort-13 Power Models                     | 3          |

|   |     | 7.4.1 CoolSort-13, Highest Clock Frequency   | 3          |

|   |     | 7.4.2 CoolSort-13, Lowest Clock Frequency    | 7          |

|   | 7.5 | CoolSort-1 Power Models                      | 8          |

|   |     | 7.5.1 CoolSort-1, Highest Clock Frequency    | 21         |

|    |       | 7.5.2   | CoolSort-1, Lowest Clock Frequency | . 125 |

|----|-------|---------|------------------------------------|-------|

|    | 7.6   | Laptop  | Power Models                       | . 126 |

|    |       | 7.6.1   | Laptop, Highest Clock Frequency    | . 129 |

|    |       | 7.6.2   | Laptop, Lowest Clock Frequency     | . 133 |

|    | 7.7   | Conclu  | usions                             | . 134 |

| 8  | Con   | clusion | s                                  | 139   |

|    | 8.1   | Future  | Work                               | . 141 |

| Bi | bliog | raphy   |                                    | 144   |

## **List of Tables**

| 2.1 | Summary of the target domains of different energy-efficiency benchmarks   |    |

|-----|---------------------------------------------------------------------------|----|

|     | and metrics.                                                              | 11 |

| 2.2 | Summary of the specifications of different energy-efficiency benchmarks   |    |

|     | and metrics.                                                              | 11 |

| 3.1 | Summary of sort benchmarks.                                               | 18 |

| 4.1 | Estimated yearly improvement in pure performance (SRecs/sec), price-      |    |

|     | performance (SRecs/\$), and energy efficiency (SRecs/J) of past Sort      |    |

|     | Benchmark winners. Performance sorts include MinuteSort, Terabyte         |    |

|     | Sort, and <i>Datamation</i> Sort                                          | 34 |

| 4.2 | Summary of commodity systems for which the JouleSort rating was exper-    |    |

|     | imentally measured                                                        | 35 |

| 4.3 | Specifications of the unbalanced commodity systems listed in Table 4.2    | 36 |

| 4.4 | JouleSort benchmark scores of unbalanced commodity systems                | 36 |

| 4.5 | Specifications of the balanced fileserver.                                | 39 |

| 4.6 | Components of the CoolSort machine and their retail prices at the time of |    |

|     | purchase                                                                  | 41 |

| 4.7 | Power and performance of winning JouleSort systems.                       | 42 |

| 4.8  | Detailed utilization information for winning JouleSort systems, including     |     |

|------|-------------------------------------------------------------------------------|-----|

|      | the number of sorted records, the sorting bandwidths and CPU utilization,     |     |

|      | and the power factor (PF).                                                    | 42  |

| 4.9  | CoolSort configurations with varying numbers of disks. For each number        |     |

|      | of disks shown in the left-hand column, the next three columns show the       |     |

|      | number of disks attached to the 4-disk controller, the 8-disk controller, and |     |

|      | the motherboard, respectively. A controller is removed from the system if     |     |

|      | no disks are attached to it                                                   | 44  |

| 4.10 | Low-power machines benchmarked by Meza et al. [45]                            | 54  |

| 6.1  | Summary of machines used to evaluate Mantis-generated models                  | 86  |

| 6.2  | Xeon server components.                                                       | 87  |

| 6.3  | Itanium server components.                                                    | 87  |

| 6.4  | CoolSort components for modeling study.                                       | 88  |

| 6.5  | Laptop components.                                                            | 88  |

| 6.6  | Selected properties of Mantis evaluation machines.                            | 89  |

| 6.7  | Descriptions of benchmarks selected to evaluate Mantis models                 | 89  |

| 6.8  | Component utilizations of Mantis evaluation benchmarks                        | 91  |

| 7.1  | Model calibration results for the Xeon server                                 | 105 |

| 7.2  | Model calibration results for the Itanium server.                             | 109 |

| 7.3  | Model calibration results for CoolSort-13 at its highest frequency 1          | 114 |

| 7.4  | Model calibration results for CoolSort-13 at its lowest frequency 1           | 118 |

| 7.5  | Model calibration results for CoolSort-1 at its highest frequency 1           | 122 |

| 7.6  | Model calibration results for CoolSort-1 at its lowest frequency 1            | 126 |

| 7.7  | Model calibration results for the laptop at its highest frequency             | 131 |

| 7.8  | Model calibration results for the laptop at its lowest frequency              | 134 |

# **List of Figures**

| 3.1 | The measured energy efficiency of the current JouleSort-winning system at  |    |

|-----|----------------------------------------------------------------------------|----|

|     | varying input sizes.                                                       | 22 |

| 4.1 | Estimated energy efficiency of previous winners of sort benchmarks         | 32 |

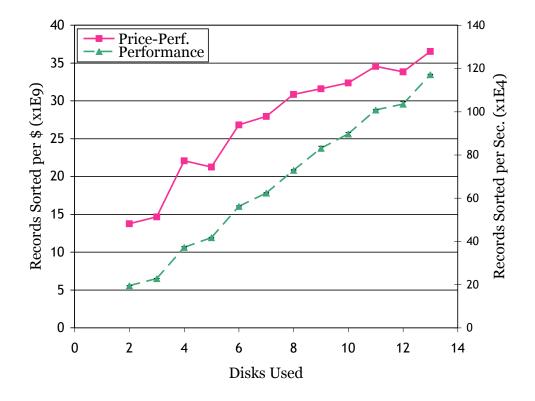

| 4.2 | Variation of performance and price-performance with the number of disks    |    |

|     | in the CoolSort system.                                                    | 45 |

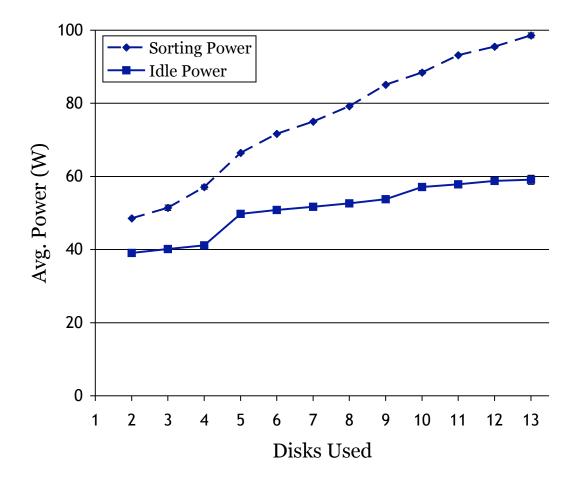

| 4.3 | Variation of power consumption with the number of disks in the CoolSort    |    |

|     | system                                                                     | 46 |

| 4.4 | Variation of energy efficiency with the number of disks in the CoolSort    |    |

|     | system                                                                     | 48 |

| 4.5 | Variation of average power and energy efficiency with CPU frequency and    |    |

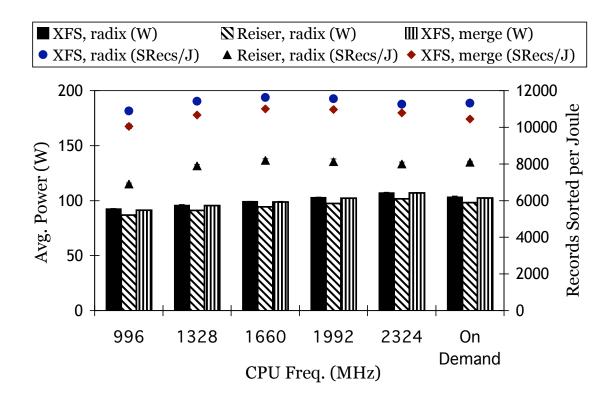

|     | filesystem for a 10 GB sort on CoolSort.                                   | 50 |

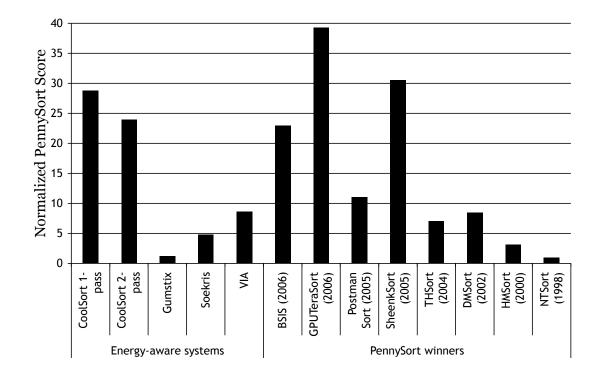

| 4.6 | PennySort scores of energy-aware systems and previous PennySort bench-     |    |

|     | mark winners, normalized to the lowest-scoring system                      | 55 |

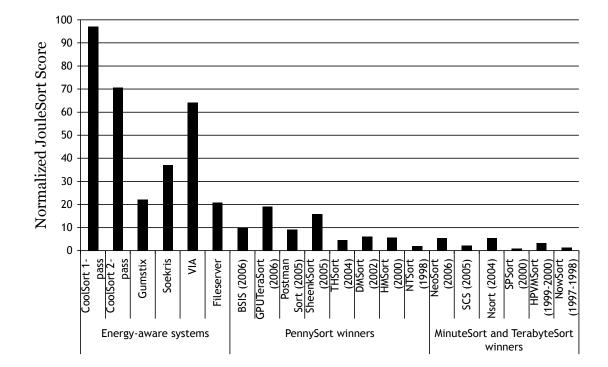

| 4.7 | JouleSort scores of energy-aware systems and previous PennySort, Min-      |    |

|     | uteSort, and Terabyte Sort benchmark winners, normalized to the lowest-    |    |

|     | scoring system.                                                            | 56 |

| 4.8 | Records sorted per Joule per dollar of purchase price of energy-aware sys- |    |

|     | tems and previous PennySort winners, normalized to the lowest-scoring      |    |

|     | system                                                                     | 57 |

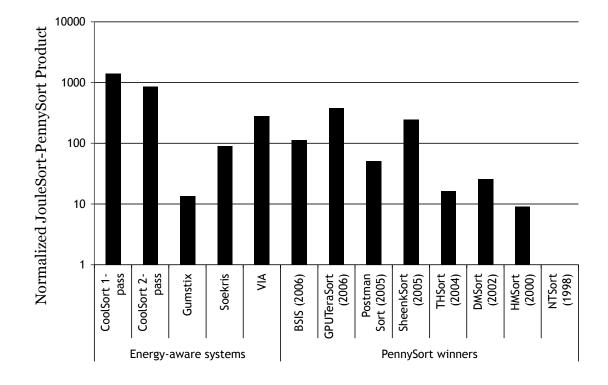

| 4.9  | Product of JouleSort and PennySort scores of energy-aware systems and                   |      |

|------|-----------------------------------------------------------------------------------------|------|

|      | previous PennySort winners, on a logarithmic scale, normalized to the                   |      |

|      | lowest-scoring system.                                                                  | 58   |

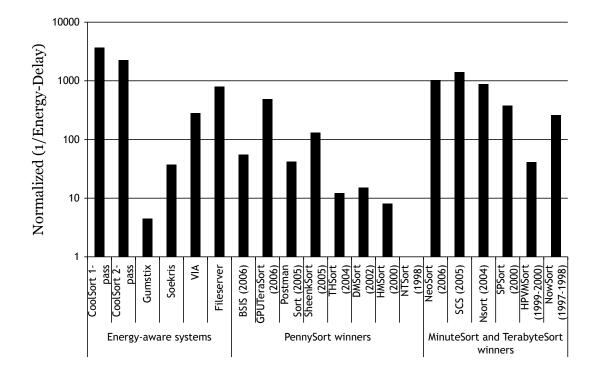

| 4.10 | Reciprocal of energy-delay product of energy-aware systems and previous                 |      |

|      | sort benchmark winners, on a logarithmic scale, normalized to the lowest-               |      |

|      | scoring system.                                                                         | 60   |

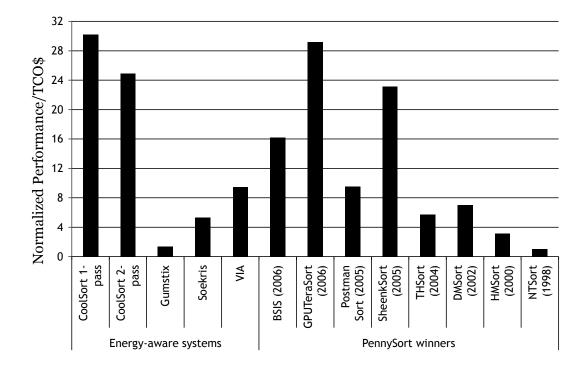

| 4.11 | Performance-TCO ratio for energy-aware systems, normalized to the                       |      |

|      | lowest-scoring system.                                                                  | 61   |

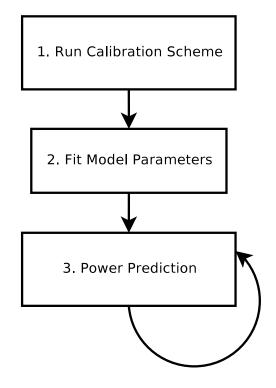

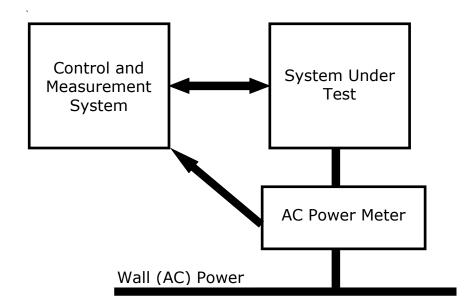

| 6.1  | Overview of Mantis model generation and use.                                            | . 78 |

| 6.2  | Mantis instrumentation setup                                                            | . 79 |

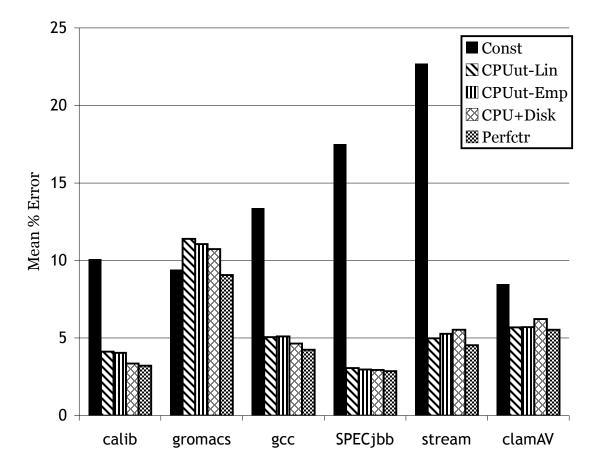

| 7.1  | Overall mean absolute error for Mantis-generated models over all bench-                 |      |

|      | marks and machine configurations                                                        | . 94 |

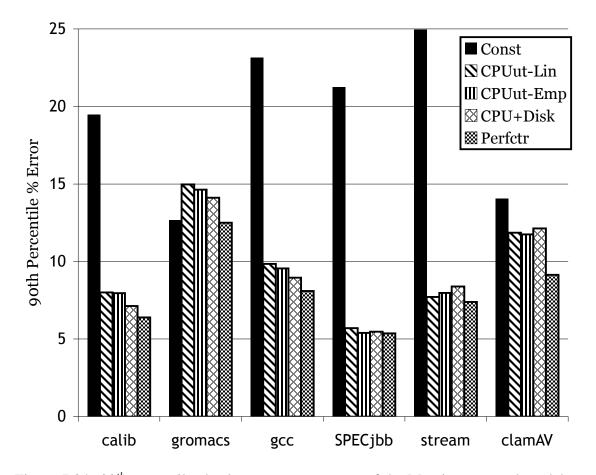

| 7.2  | Overall 90 <sup>th</sup> percentile absolute error for Mantis-generated models over all |      |

|      | benchmarks and machine configurations                                                   | 95   |

| 7.3  | Best case for the empirical CPU-utilization-based model: CPU-intensive                  |      |

|      | benchmarks on Xeon server.                                                              | . 96 |

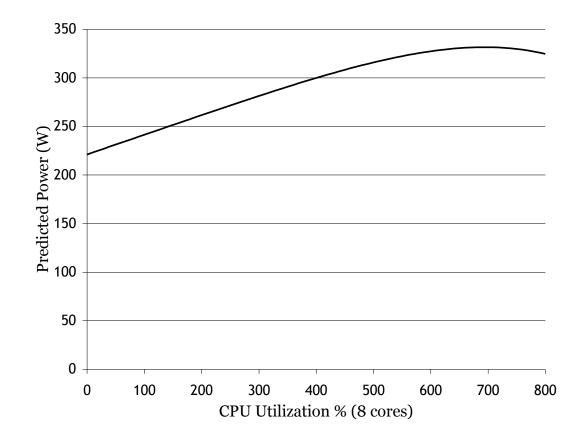

| 7.4  | Power predicted by the empirical CPU-utilization-based model versus CPU                 |      |

|      | utilization for the Xeon server.                                                        | . 97 |

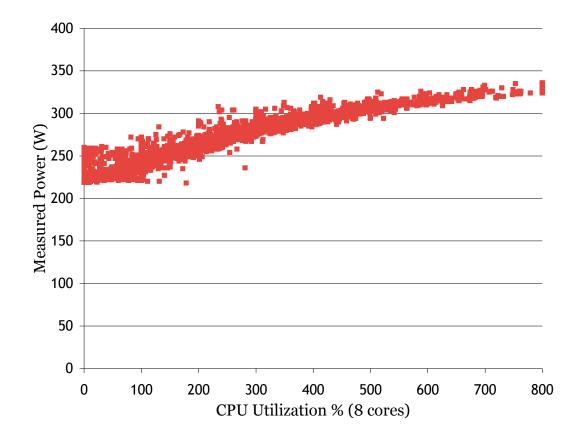

| 7.5  | Measured power versus CPU utilization for the Xeon server during the cal-               |      |

|      | ibration suite. Note that memory and disk utilization also varied over this             |      |

|      | data                                                                                    | . 98 |

| 7.6  | Best case for the CPU- and disk-utilization-based model: Selected bench-                |      |

|      | marks on CoolSort-13 at the highest frequency.                                          | 100  |

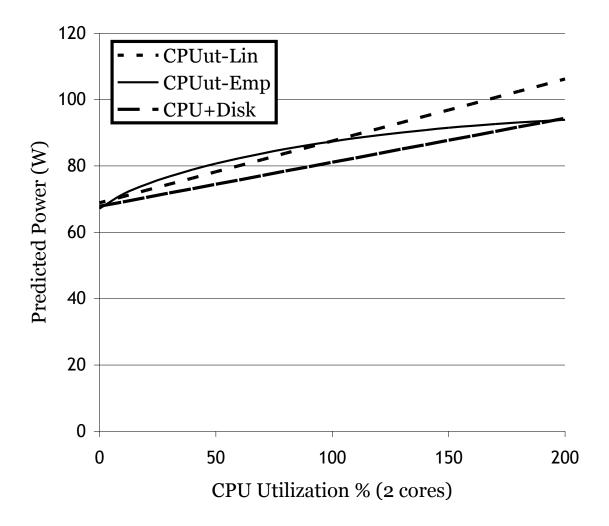

| 7.7  | Power predicted by the CPU-utilization-based models and the CPU and                     |      |

|      | disk-utilization-based model versus CPU utilization on CoolSort-13 at its               |      |

|      | highest frequency. Disk utilization is assumed to be 0                                  | 101  |

| 7.8  | Best case for the performance-counter-based model: Selected benchmarks               |

|------|--------------------------------------------------------------------------------------|

|      | on the Xeon server and on CoolSort-13 at the highest frequency 103                   |

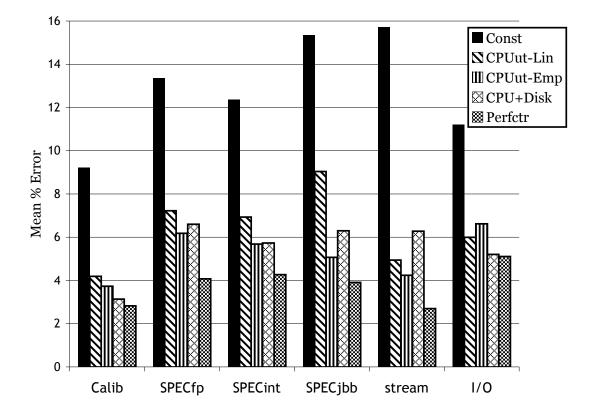

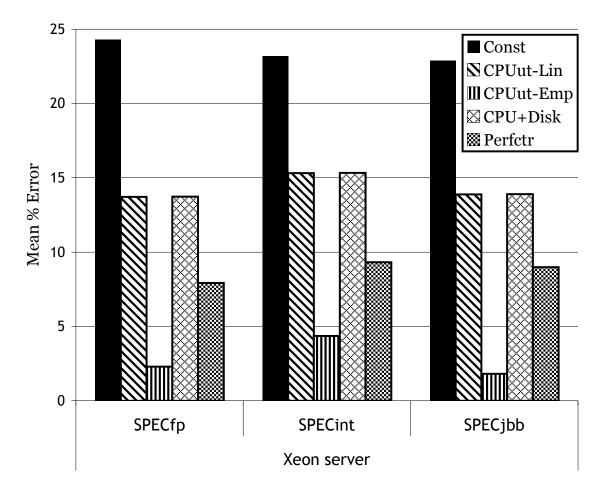

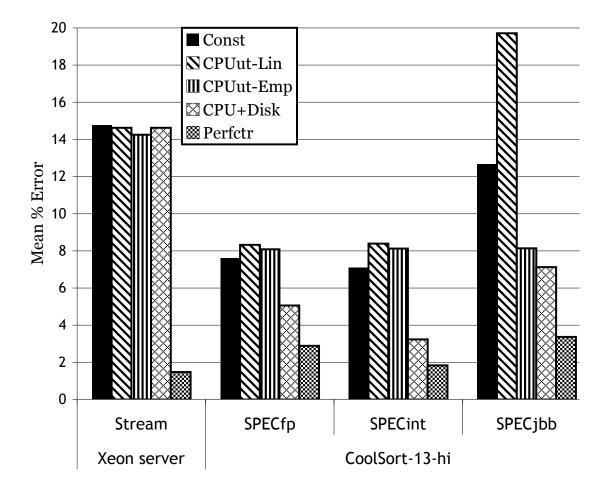

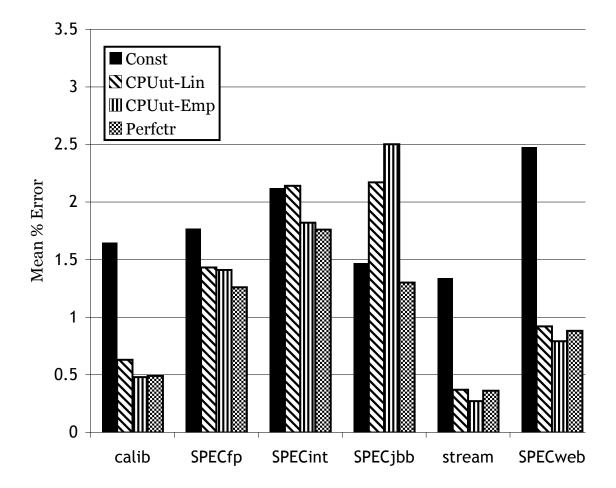

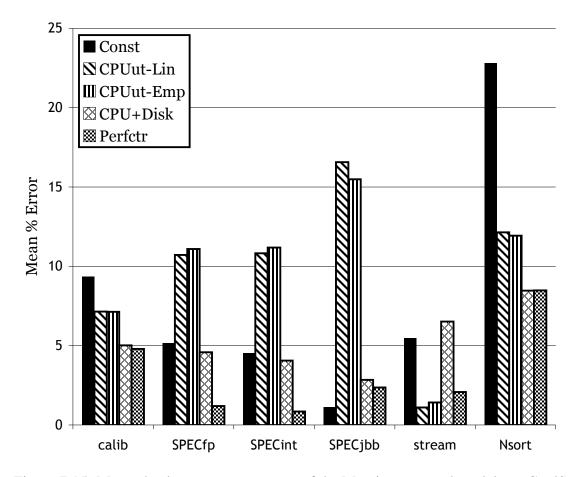

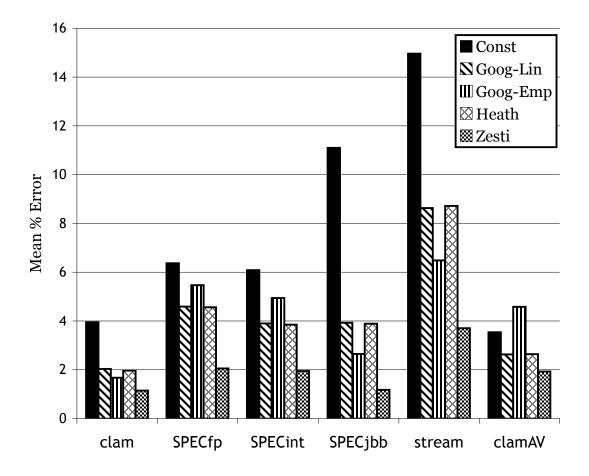

| 7.9  | Mean absolute percentage error of the Mantis-generated models on the                 |

|      | Xeon server                                                                          |

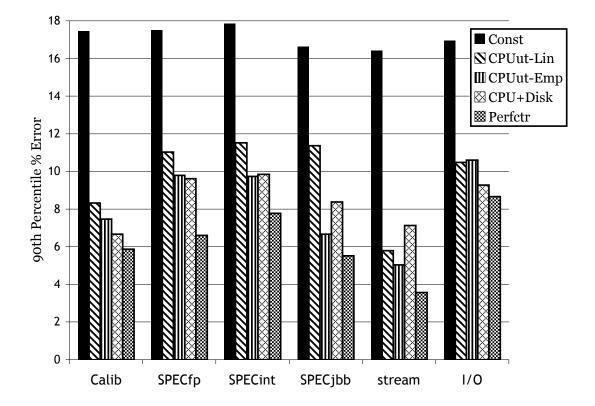

| 7.10 | 90 <sup>th</sup> percentile absolute percentage error of the Mantis-generated models |

|      | on the Xeon server                                                                   |

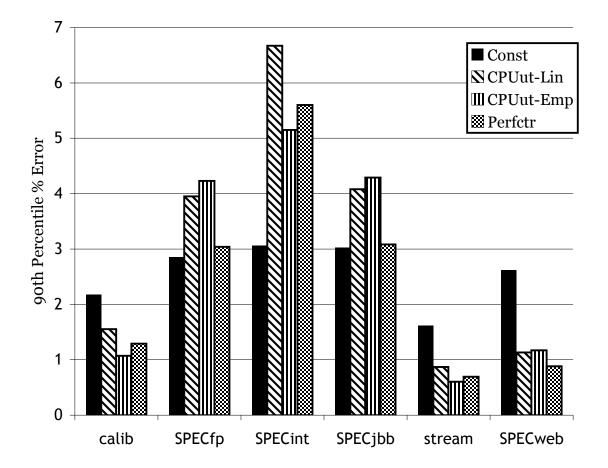

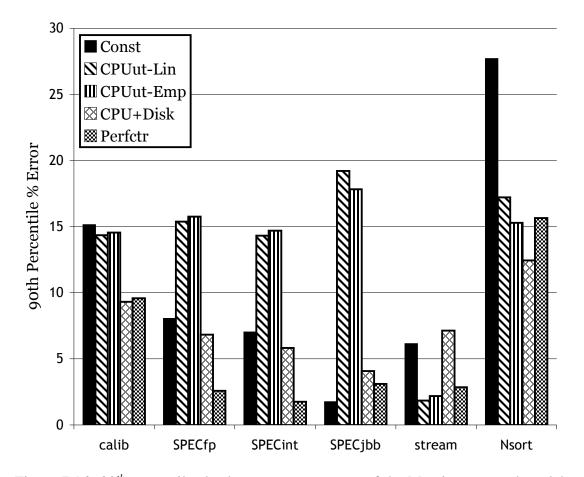

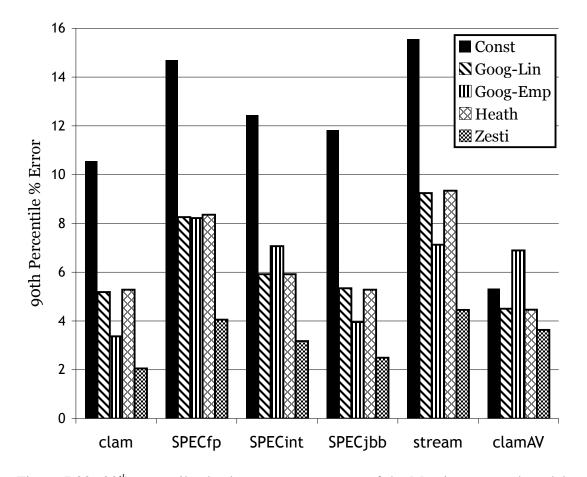

| 7.11 | Mean absolute percentage error of the Mantis-generated models on the Ita-            |

|      | nium server                                                                          |

| 7.12 | 90 <sup>th</sup> percentile absolute percentage error of the Mantis-generated models |

|      | on the Itanium server                                                                |

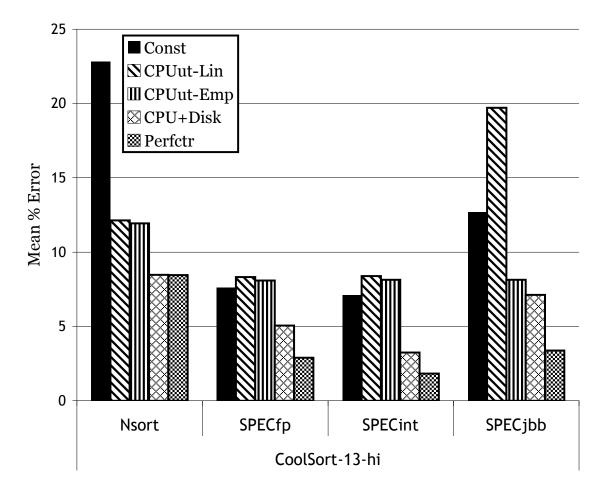

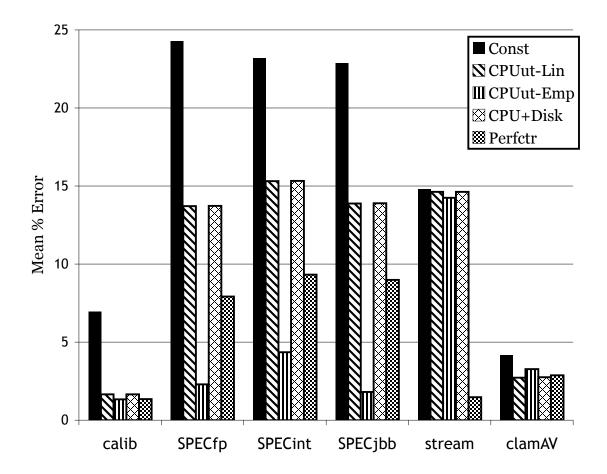

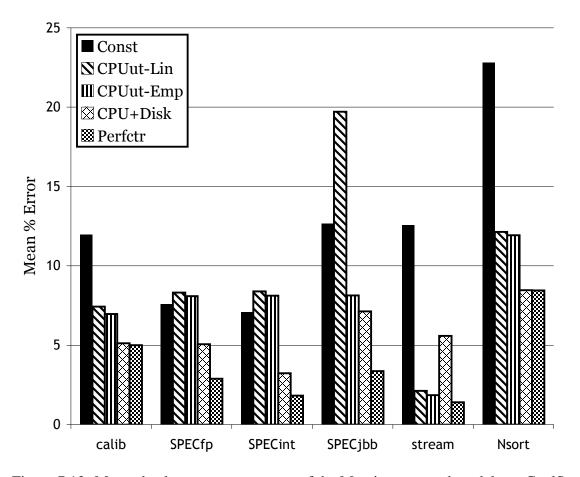

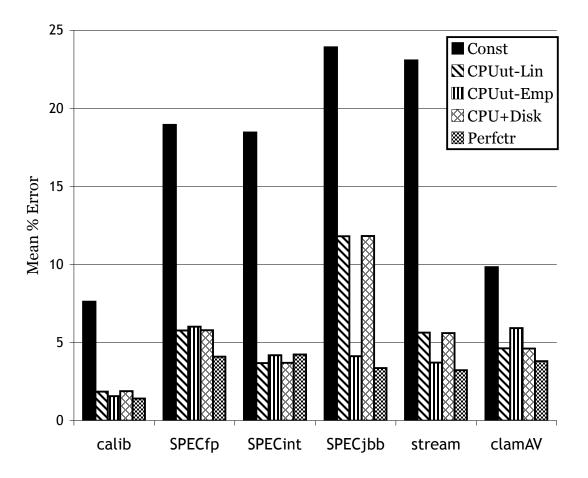

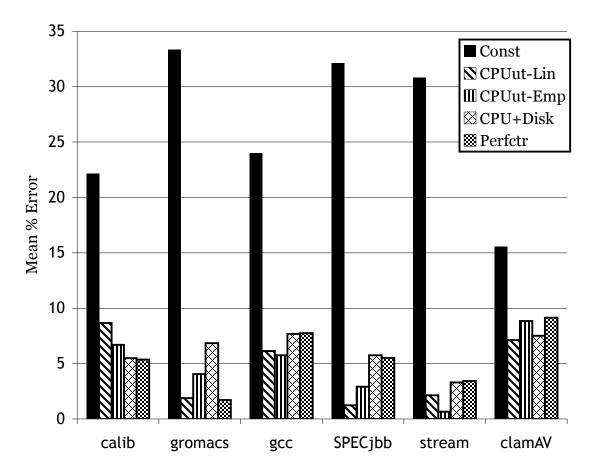

| 7.13 | Mean absolute percentage error of the Mantis-generated models on                     |

|      | CoolSort-13 at its highest frequency                                                 |

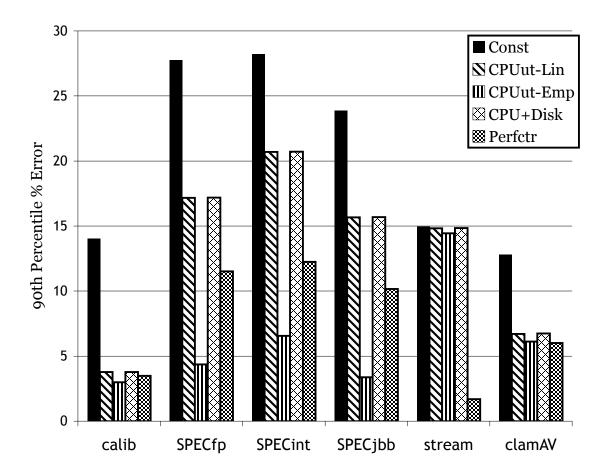

| 7.14 | 90 <sup>th</sup> percentile absolute percentage error of the Mantis-generated models |

|      | on CoolSort-13 at its highest frequency                                              |

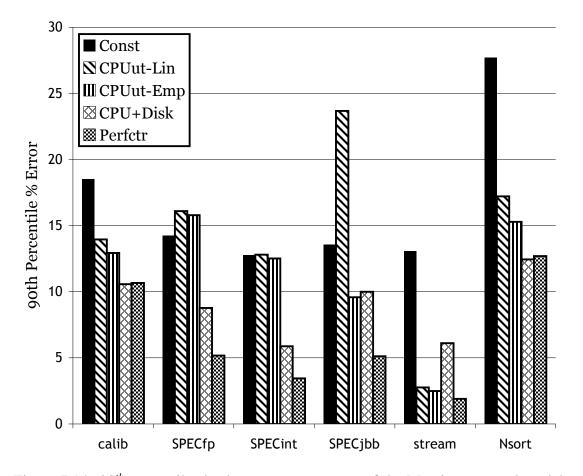

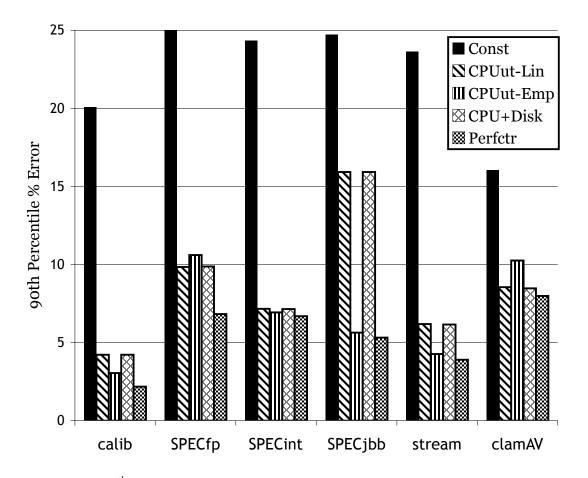

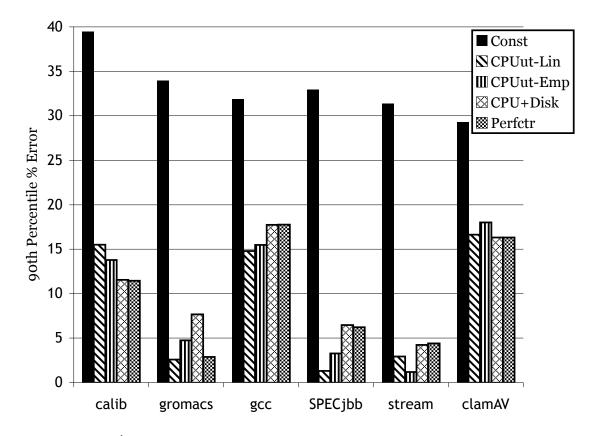

| 7.15 | Mean absolute percentage error of the Mantis-generated models on                     |

|      | CoolSort-13 at its lowest frequency                                                  |

| 7.16 | 90 <sup>th</sup> percentile absolute percentage error of the Mantis-generated models |

|      | on CoolSort-13 at its lowest frequency                                               |

| 7.17 | Mean absolute percentage error of the Mantis-generated models on                     |

|      | CoolSort-1 at its highest frequency                                                  |

| 7.18 | 90 <sup>th</sup> percentile absolute percentage error of the Mantis-generated models |

|      | on CoolSort-1 at its highest frequency                                               |

| 7.19 | Mean absolute percentage error of the Mantis-generated models on                     |

|      | CoolSort-1 at its lowest frequency                                                   |

| 7.20 | 90 <sup>th</sup> percentile absolute percentage error of the Mantis-generated models |

|      | on CoolSort-1 at its lowest frequency                                                |

| 7.21 | Mean absolute percentage error of the Mantis-generated models on the lap-            |    |

|------|--------------------------------------------------------------------------------------|----|

|      | top at its highest frequency                                                         | 31 |

| 7.22 | 90 <sup>th</sup> percentile absolute percentage error of the Mantis-generated models |    |

|      | on the laptop at its highest frequency                                               | 32 |

| 7.23 | Mean absolute percentage error of the Mantis-generated models on the lap-            |    |

|      | top at its lowest frequency                                                          | 35 |

| 7.24 | 90 <sup>th</sup> percentile absolute percentage error of the Mantis-generated models |    |

|      | on the laptop at its lowest frequency                                                | 36 |

# Chapter 1

# Introduction

#### **1.1 Motivation**

In contexts ranging from large-scale data centers to mobile devices, energy use is an important concern. In data centers, according to the United States Environmental Protection Agency, power consumption in the United States doubled between 2000 and 2006, and will double again in the next five years [74]. Server power consumption not only directly affects a data center's energy costs, but also necessitates the purchase and operation of cooling equipment, which can consume one-half to one Watt for every Watt of power consumed by the computing equipment.

In addition, energy use has implications for reliability, density, and scalability. As data centers house more servers and consume more energy, removing heat from the data center becomes increasingly difficult [49]. Since the reliability of servers and disks decreases at high temperatures, the power consumption of servers and other components limits the achievable density of data centers, which in turn limits their scalability. Furthermore, energy use in data centers is starting to prompt environmental concerns of pollution and excessive load placed on local utilities [51]. These concerns are sufficiently severe that large companies are starting to build data centers near electric plants in cold-weather environments [42].

In mobile devices, battery capacity and energy use directly affect usability. Battery capacity determines how long devices last, constrains form factors, and limits functionality. Since battery capacity is limited and improving slowly, device architects have concentrated on extracting greater efficiency from the individual underlying components, such as the processor, the display, and the wireless subsystems.

To facilitate energy-efficiency optimizations, we need *metrics* and *models*. *Metrics* help define energy efficiency, giving a basis on which to compare designs and a way to identify promising energy-efficient technologies. *Models* show the relationship between resource

utilization and power consumption, which allows data center scheduling algorithms or individual users to tailor their usage to maximize energy efficiency.

To address these challenges, this dissertation presents the JouleSort energy-efficiency benchmark and the Mantis approach to high-level power modeling.

### **1.2** Contributions

The main contributions of this dissertation are the following:

- It presents the specification for JouleSort, the first completely specified, full-system energy-efficiency benchmark to be proposed. It describes the benchmark workload, metric, and rules, highlighting the unique challenges of designing a benchmark for energy efficiency.

- It presents the energy-efficient CoolSort system, the machine with the highest known JouleSort benchmark score, which is over 3.5 times more energy-efficient than previous systems. CoolSort consists of a high-end mobile processor connected to 13 SATA laptop disks. This unusual configuration suggests a promising new approach to energy-efficient hardware design. The CoolSort design and the JouleSort specification were originally presented in [57] and [58].

- It presents a method of high-level, full-system power modeling that uses a linear combination of OS utilization metrics and hardware performance counters, and demonstrates that this model accurately predicts power consumption over a very wide range of hardware configurations and software workloads. This model was originally presented in [14].

- It provides a detailed evaluation of several previously proposed high-level power models, noting the types of systems to which each model is best suited and the trade-offs between model complexity and prediction accuracy. This analysis shows that the

modeling approach we proposed, based on OS utilization metrics and performance counters, is the most accurate type of model across the machines and workloads tested. It is particularly useful for machines whose dynamic power consumption is not dominated by the CPU and for machines with aggressively power-managed CPUs, two classes of systems that are increasingly prevalent.

#### **1.3 Dissertation Outline**

Chapters 2 through 4 present the JouleSort energy-efficiency benchmark. Chapter 2 provides background on the problem of benchmarking for energy efficiency, examining the goals of an energy-efficiency benchmark and the limitations of previous approaches.

Chapter 3 presents the specification for the JouleSort benchmark, which was the first completely specified, full-system energy-efficiency benchmark to be proposed. It explains the JouleSort workload, metric, and rules, as well as the challenges and pitfalls of designing a fair benchmark for energy efficiency.

Chapter 4 presents the CoolSort machine, an energy-efficient sorting system that achieves the highest known JouleSort score. It also evaluates the JouleSort benchmark scores of a variety of other systems, including the best-performing and most cost-efficient winners of previous sort benchmarks, as well as commodity machines from a variety of system classes. Finally, it compares the JouleSort metric to metrics using other combinations of performance, cost, and power. Different combinations of these metrics favor different system classes, but the high score of the CoolSort machine is not highly sensitive to changes in the metric.

Chapters 5 through 7 describe the Mantis approach to portable and general high-level full-system power modeling. Chapter 5 defines the goals of the Mantis approach and examines previous approaches to power modeling at the architectural level and higher, from

#### CHAPTER 1. INTRODUCTION

detailed simulation-based power models to very simple high-level models based on a single metric. It compares the accuracy, generality, and level of detail of these previously proposed models, and assesses their suitability with respect to the Mantis goals.

Chapter 6 explains the Mantis model generation and evaluation methodology. It describes the models themselves as well as the process of generating the models, including a detailed discussion of the software calibration suite and the hardware infrastructure. It also details the hardware and software configurations on which the models are evaluated in Chapter 7.

Chapter 7 presents the results of generating and evaluating the Mantis models on a wide range of machines. In general, the model that we proposed, which uses a linear combination of CPU performance counters and OS-reported component utilizations, is most accurate. We show the strengths and limitations of each model and make a case that OS-reported CPU utilization alone will be an increasingly less useful proxy for system-level power consumption in the future. Finally, Chapter 8 concludes the dissertation and suggests directions for future work.

Chapter 2

**Benchmarking Energy Efficiency**

Energy efficiency is a pressing concern in computer systems, from mobile devices to data centers. Energy-conscious users, as well as computer manufacturers and researchers, need to be able to assess and compare the energy efficiency of computer systems in order to make purchasing decisions or to identify promising technologies. Well-defined benchmarks are needed to provide standardized and fair comparisons of computers' energy efficiency. To this end, this thesis presents the JouleSort energy-efficiency benchmark in Chapter 3. This chapter lays the groundwork by explaining the challenges and complexities of energy-efficiency benchmarking, outlining the goals of the JouleSort benchmark, and describing the goals and limitations of other energy-efficiency benchmarks and metrics that have been proposed.

#### 2.1 Benchmarking Challenges

A complete benchmark specifies three things: a *workload* to run, which should represent some real-world task of interest; a *metric* or "score" to compare different systems; and operational *rules* to ensure that the benchmark runs under realistic conditions. Creating a benchmark for energy efficiency shares some challenges with creating any benchmark. There is the question of what to benchmark, *e.g.* components, single machines, or data centers. There is also the question of workload choice, which effectively also determines the class of machines to which the benchmark can be applied; for example, a supercomputing benchmark probably could not run on handheld devices, and would not be a representative workload if it could. Benchmarks exist for almost every conceivable class of workload and for every class of machine, from small embedded processors [15] to large clusters [72] and supercomputers [54].

The benchmark metric must also be determined. Even when the goal is to measure pure performance, the decision of whether to use a metric based on the time to execute a fixedsize workload or the throughput in a fixed amount of time can bias the metric toward certain types of machines or exclude them entirely. When the goal is to balance performance with another concern, such as cost, the question of how to weigh and combine the two metrics in the final benchmark score adds another element of complexity.

Finally, the benchmark specification must include rules to ensure that the benchmark runs under fair and realistic conditions. For performance-oriented benchmarks, these rules often constrain the types of compiler optimizations that can be applied to the benchmark source code in order to preclude benchmark-specific compiler optimizations of dubious general correctness. The rules may also constrain the type of hardware, operating system, or file system on which the benchmark is run.

Benchmarking energy efficiency presents some unique challenges. The choice of workload is complicated by the fact that the desired operating point(s) of the system must be identified; in particular, since lightly utilized systems are currently highly inefficient [5], benchmark designers may want to target this operating point. The choice of metric also becomes more complex, since it must resolve the question of how to weigh performance against power consumption. However, the benchmark rules are the largest source of increased complexity. First, the definition of the system and its environment becomes more complex. The ambient temperature around the system affects its power consumption, so benchmark designers may want to regulate it. They also must decide whether or not to include the cooling systems of both the machine and the building housing it, a significant decision since cooling can consume up to one Watt for each Watt of power consumed by the computing equipment [50]. Additionally, energy-efficiency benchmarks require standards to govern the accuracy and sampling rate of the power and temperature instrumentation.

#### 2.2 Energy-Efficiency Benchmark Goals

The JouleSort benchmark was created with the goal of providing a fully specified energyefficiency benchmark that was meaningful and broadly applicable in order to identify trends and inspire improvements in energy efficiency. This section describes the design criteria that the JouleSort specification seeks to balance.

**Power-performance trade-off**: The benchmark's metric should capture a system's performance as well as some measure of power use. Peak or average power would be an impractical metric, since neither includes a measurement of performance; the benchmark should not reward a system that consumes almost no power and completes almost no work. Two reasonable alternatives for the metric are energy, which is the product of execution time and power; and the energy-delay product. The former metric weighs performance and power equally, while the latter places more emphasis on performance. Since many benchmarks already emphasize performance, we chose to use energy as the metric in order to draw attention to power consumption.

**Peak efficiency:** A benchmark can measure systems at their most energy-efficient operating point, which corresponds to peak utilization for most computer systems [5], or it can explicitly specify one or more different operating points, as SPECpower\_ssj [68] does. For simplicity of benchmarking and clarity of the benchmark score, our benchmark does not specify an operating point and therefore measures peak energy efficiency, giving an upper bound on the work that can be done for a given power consumption. This operating point influences design and provisioning constraints for data centers as well as mobile devices. Furthermore, peak utilization is the most common operating point in some computing domains, such as enterprise environments that use server consolidation to improve energy efficiency, as well as scientific computing.

**Holistic** and **Balanced:** A single component cannot accurately reflect the overall performance and power characteristics of a system. Therefore, the workload should exercise all core components and stress them roughly equally. The benchmark metric should incorporate the energy used by all core components.

**Inclusive** and **Portable:** The benchmark should be able to assess the energy efficiencies of a wide variety of systems: PDAs, laptops, desktops, servers, clusters, and so on.

It should be as unbiased as possible among architectures and system classes. Moreover, the benchmark's workload should be implementable and meaningful across all of these platforms.

**History-proof:** In order to track improvements over generations of systems and identify promising new technologies, the benchmark specification should remain meaningful as hardware and software technologies evolve, and it should allow comparisons across different generations of systems.

**Representative:** The benchmark's workload should represent an important class of workloads for the systems being benchmarked.

**Simple:** The benchmark should be as simple as possible to set up and administer, and the score should be easy to understand.

The next section evaluates current energy-efficiency benchmarks in light of these goals.

#### 2.3 Current Energy-Efficiency Metrics

An ideal benchmark for energy efficiency would consist of a universally relevant workload that is portable to any computing device; a metric that balances power and performance in a universally appropriate way; and rules that are impossible to circumvent and that provide fair comparisons across every class of machine. This ideal is impossible to achieve in practice, so proposed metrics have specialized in different classes of workloads and systems. This section describes previously proposed energy-efficiency benchmarks and metrics. Table 2.1 shows the target system classes of these metrics, and Table 2.2 summarizes their specifications.

#### **2.3.1** Component-level Benchmarks and Metrics

At the processor level, Gonzalez and Horowitz argued in 1996 that the energy-delay product was the appropriate metric for comparing two designs [20]. They observed that a chip's

| Benchmark                 | Level       | Domain                      |

|---------------------------|-------------|-----------------------------|

| EnergyBench               | Processor   | Embedded                    |

| SWaP                      | System(s)   | Enterprise                  |

| Energy Star certification | System      | Mobile, desktop, enterprise |

| SPECpower_ssj             | System      | Enterprise                  |

| Compute Power Efficiency  | Data center | Enterprise                  |

| Green Grid metrics        | Data center | Enterprise                  |

Table 2.1: Summary of the target domains of different energy-efficiency benchmarks and metrics.

| Benchmark       | Workload              | Metric                             |

|-----------------|-----------------------|------------------------------------|

| SWaP            | Unspecified           | Performance/(Space $\times$ Watts) |

| EnergyBench     | EEMBC benchmarks      | Throughput/Joule                   |

| Energy Star:    | Sleep, idle, standby, | Certify if "typical" power         |

| workstations    | Linpack, SPECviewperf | < 35% of max. power                |

| Energy Star:    | Sleep, idle,          | Certify if each mode's             |

| other systems   | standby modes         | power < predefined threshold       |

| SPECpower_ssj   | Server-side Java      | Operations/Watt                    |

|                 | under varying loads   | averaged over all loads            |

| Green Grid DCD  | Unspecified           | Equipment power / floor            |

|                 |                       | area $(kW/ft^2)$                   |

| Green Grid DCiE | Unspecified           | % of facility power                |

|                 |                       | reaching IT equipment              |

| Compute Power   | Unspecified           | IT equipment util. × DCiE          |

| Efficiency      |                       |                                    |

| Green Grid DCeP | Unspecified           | Work done / facility power         |

Table 2.2: Summary of the specifications of different energy-efficiency benchmarks and metrics.

performance and power consumption were both directly related to the clock frequency, with performance directly proportional to, and power consumption increasing as the square of, clock frequency. Therefore, decreasing a processor's clock frequency by a factor of x would result in performance degradation proportional to x and a decrease in power consumption proportional to  $x^2$ . Since energy is the product of execution time and average power, the net effect would be an energy decrease by a factor of x. Comparing processors based on energy would therefore motivate processor designers to focus solely on lowering clock frequency at the expense of performance. On the other hand, the energy-delay product, which weighs power against the square of execution time, would show the underlying design's energy efficiency rather than merely reflecting the clock frequency. This metric is a specific case of the *MIPS*<sup> $\gamma$ </sup> per Watt metric [79], where the choice of  $\gamma$  reflects the desired balance between performance and power. In any case, these metrics are focused on the processor and do not provide a suggested workload.

For embedded processors, the Embedded Microprocessor Benchmark Consortium (EEMBC) has proposed the EnergyBench benchmarks [16]. EnergyBench provides a standardized data acquisition infrastructure for measuring processor power when running one of EEMBC's existing performance benchmarks. Benchmark scores are then reported as "Netmarks per Joule" for networking benchmarks and "Telemarks per Joule" for telecommunications benchmarks. This benchmark is focused solely on the processor and on the embedded domain.

#### 2.3.2 System-level Benchmarks and Metrics

Several metrics and benchmarks have been proposed at the single-system level. Performance per Watt became a popular metric for servers once power became an important design consideration [37]. Performance is typically specified with either MIPS or the rating from peak-performance benchmarks like SPECint [64] or TPC-C [72]. Sun Microsystems has proposed the SWaP (Space, Watts, and Performance) metric to include servers' space efficiency as well as power consumption [71].

Two evolving standards in system-level energy efficiency are the United States government's Energy Star certification guidelines for computers, and the SPECpower\_ssj benchmark.

Energy Star is a designation given by the U.S. government to highly energy-efficient household products, which has recently been expanded to include computers [17]. For desktops, desktop-derived servers, notebooks, and game consoles, the Energy Star certification is awarded to systems with idle, sleep, and standby power consumptions below certain specified thresholds. For workstations, however, Energy Star certification requires that the "typical" power (a weighted function of the idle, sleep, and standby power consumptions) not exceed 35% of the "maximum power" (the power consumed during the Linpack and SPECviewperf benchmarks, plus a factor based on the number of installed hard disks). Energy Star certification also requires that a system's power supply efficiency exceed 80%. Energy Star certification thus depends mainly on a system's low-power states and does not include a measure of the system's performance. Furthermore, its score is coarse-grained; a system is either certified, or it is not.

The SPECpower\_ssj benchmark, released in December 2007, is designed to assess the energy efficiency of servers under a wide variety of loads [68]. Data center servers usually operate far below peak utilization, which creates inefficiencies, since peak utilization is the most efficient operating point for modern servers [5]. Therefore, SPECpower\_ssj uses a CPU-intensive server-side Java workload and scales it to run at 10%, 20%, 30%, 40%, 50%, 60%, 70%, 80%, 90%, and peak utilization. The SPECpower\_ssj score is the overall number of operations per Watt across all of these utilization modes. The benchmark also specifies a minimum ambient temperature and standards for the power and temperature sensors used to collect the data. This benchmark is CPU- and memory-centric, and both its workload and metric are tailored to the data center domain.

#### **2.3.3** Data Center-level Benchmarks and Metrics

Many metrics have been proposed to quantify various aspects of data center energy efficiency, from the building's power and cooling provisioning to the utilization of the computing equipment. The Uptime Institute identified a variety of metrics contributing to data center "greenness," including measures of power conversion efficiency at the server and data center levels, as well as the utilization efficiency of the deployed hardware [70]. To optimize data center cooling, Chandrakant Patel and others have advocated a metric based on performance per unit of *exergy* destroyed [49]. Exergy is the available energy in a thermodynamic sense, and so exergy-aware metrics take into account the conversion of energy into different forms. In particular, exergy is expended when electrical power is converted to heat and when heat is transported across thermal resistances.

The Green Grid, an industrial consortium including most major hardware vendors, has proposed several metrics to quantify data center power efficiency over both space and time. To quantify space efficiency, they define the Data Center Density (DCD) metric as the ratio of the power consumed by all equipment on the raised floor to the area of the raised floor, in units of kilowatts per square foot [23]. To quantify time efficiency (that is, energy efficiency), they propose the Data Center Infrastructure Efficiency (DCiE) metric [22]. DCiE is defined as the percentage of the total facility power that goes to the "IT equipment" (primarily compute, storage, and network). Since IT equipment power is not necessarily a proxy for performance, two extensions of this metric have been proposed. Compute Power Efficiency (CPE), proposed by Malone and Belady, scales the DCiE by the IT equipment utilization, a value between 0 and 1 [41]. With this metric, the power consumed by idle servers counts as overhead rather than as power that is being productively used. Similarly, the Green Grid has introduced the Data Center Energy Productivity metric (DCeP), which is the useful work divided by the total facility power [24]. This metric can be applied to

any data center workload. None of these data center metrics specifies a workload, and most do not take any measure of performance into account.

#### 2.3.4 Summary

Each of these metrics is useful in evaluating energy efficiency in a particular context, from embedded processors to underutilized servers to entire data centers. However, energy efficiency metrics for many important computing domains have not been methodically addressed, and none of the benchmarks or metrics described in this section fully addresses the goals set forth in Section 2.2. The next chapter presents the specification of the Joule-Sort energy-efficiency benchmark, which was the first completely specified full-system energy efficiency benchmark, and which remains the only energy-efficiency benchmark for data-intensive computing.

# Chapter 3

# **The Joulesort Benchmark Definition**

This chapter presents the specification for JouleSort, a full-system, data-intensive benchmark applicable to systems from low-power mobile devices to large clusters. It describes JouleSort's workload, metric, and energy measurement guidelines, noting the pitfalls of alternative approaches.

#### 3.1 Workload

The workload for the JouleSort benchmark is external sort, as specified by the Sort Benchmark website [62]. External sort has been an important benchmark in the database community since 1985 [1], and researchers have used it to understand the system-level effectiveness of algorithm and component improvements, as well as to identify promising technology trends. Previous sort benchmark winners have foreshadowed the transition from supercomputers to shared-memory multiprocessors to commodity clusters, and have recently demonstrated the promise of general-purpose computation on graphics processing units (GPUs) [21]. The sort benchmarks have historically been used as a bellwether to illuminate the potential of new technologies, rather than to guide purchasing decisions.

The sort benchmarks currently have three active categories, summarized in Table 3.1. PennySort is a price-performance benchmark that measures the number of records a system can sort for one penny, assuming a 3-year depreciation; its Performance-Price Sort variation sets a fixed time budget of one minute and compares records sorted per dollar. MinuteSort and Terabyte Sort measure a system's pure performance in sorting for a fixed time of one minute and a fixed data set of one terabyte, respectively. The original sort benchmark, *Datamation* Sort [1], was a pure-performance benchmark for a fixed data set of one million records; it is now deprecated, since this task is trivial on modern systems. A JouleSort benchmark to measure the power-performance trade-off is thus a logical addition to the sort benchmark suite.

| Benchmark       | Focus       | Description                    | Status     |

|-----------------|-------------|--------------------------------|------------|

| Datamation Sort | Perf.       | Sort 1 million records         | Deprecated |

|                 |             | in minimum time                |            |

| MinuteSort      | Perf.       | Sort max. records in 1 minute  | Active     |

| Terabyte Sort   | Perf.       | Sort 1 TB of data (10 billion  | Active     |

|                 |             | records) in minimum time       |            |

| Price-Perf.     | Cost-perf.  | Sort max. records in 1 minute  | Inactive   |

| Sort            |             | and compute records/\$         |            |

| PennySort       | Cost-perf.  | Sort as many records as        | Active     |

|                 |             | possible for 1 cent, assuming  |            |

|                 |             | 3-year depreciation            |            |

| JouleSort       | Power-perf. | Sort a fixed number of records | Active     |

|                 |             | (approx. 10 GB, 100 GB,        |            |

|                 |             | 1 TB) with minimum energy      |            |

Table 3.1: Summary of sort benchmarks.

The sort benchmarks' workload can be summarized as follows: sort a file consisting of randomly permuted 100-byte records with 10-byte keys. The input file must be read from, and the output file written to, external nonvolatile storage. The output file must be newly created rather than reusing the input file, and all intermediate files used by the sort program must be deleted.

This workload is *representative* because most platforms, from large to small, must manage an ever-increasing supply of data [40] and thus all perform some type of I/O-centric task. For example, large-scale websites run parallel analyses over voluminous log data across thousands of machines [13]. Laptops and servers contain various kinds of file systems and databases and perform sequential I/O-intensive tasks such as backups and virus scans. In the handheld domain, cell phones, personal digital assistants, and cameras store, retrieve, and process multimedia data from flash memory.

Since the sort benchmarks have been implemented on clusters, supercomputers, multiprocessors, and personal computers [62], sort is clearly *portable* and *inclusive*. It is a *simple* workload to understand and implement. It is also *holistic* and *balanced*, stressing the core components of I/O, memory, and the CPU, as well as the interfaces that connect them. Because the fastest sorts tend to run most components at near-peak utilization, sort measures a system at *peak energy efficiency*. Finally, the sort workload is relatively *history-proof*. While the size of the data set has changed over time, the fundamental sorting task has been the same since the original sort benchmark was proposed in 1985 [1].

# 3.2 Metric

Designing a metric that allows fair comparisons across systems and avoids loopholes that obviate the benchmark presents a major challenge in benchmark development. Since the JouleSort benchmark's metric should give power and performance equal weight (see Section 2.2), there are three ways to define the benchmark score:

- Set a fixed energy budget for the sort, and compare systems based on the number of records sorted without exceeding that budget.

- Set a fixed time budget for the sort, and compare systems based on the ratio of records sorted to energy consumed within that time budget, expressed in sorted records per Joule.

- Set a fixed workload size for the sort, and compare systems based on the amount of energy consumed while sorting.

This section examines these three possibilities in detail, and explains the decision to choose a fixed workload size for JouleSort.

## **3.2.1** Fixed Energy Budget

The most intuitive extension of MinuteSort and PennySort is to fix a budget for energy consumption, and then compare the number of records sorted by different systems while

staying within that energy budget. This approach has two drawbacks. First, the power consumption of current platforms varies by several orders of magnitude, from less than 1 W for handhelds to over 1000 W for large servers, and much more for clusters or supercomputers. If the fixed energy budget is too small, larger configurations will only sort for a fraction of a second; if the energy budget is more appropriate to larger configurations, smaller configurations will run out of external storage. To be fair and inclusive, the benchmark would need to have multiple budgets and categories for different classes of systems and would need these classes to be updated as the technology changes. This decision would limit the benchmark's ability to be *inclusive* and *history-proof*.

Second, and more important from a practical benchmarking perspective, finding the largest data set that fits into an energy budget is a non-trivial task due to unavoidable measurement error. There are inaccuracies in synchronizing readings from a power meter to the actual runs and from the power meter readings themselves (+/- 1.5% for the one used in these experiments). Since energy is the product of power and execution time, it is affected by variation in both quantities, so this choice is not *simple*.

## **3.2.2** Fixed Time Budget

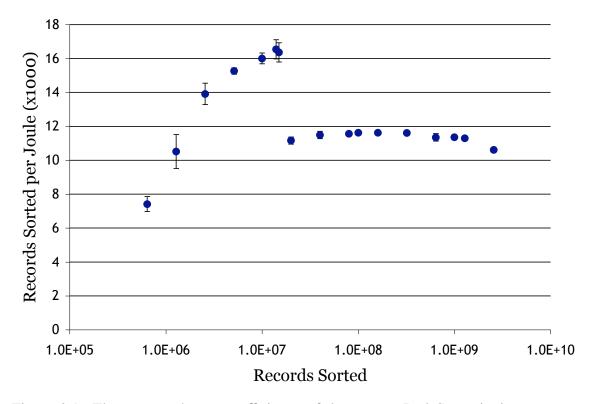

Analogous to the MinuteSort and Price-Performance Sort metrics, the JouleSort benchmark could specify a fixed time budget, with a metric based on the number of records sorted and the power consumption within that time. Just as MinuteSort's metric is the number of sorted records and Price-Performance Sort's is the number of sorted records per dollar, the JouleSort metric would be the number of sorted records per Joule. This benchmark would not require separate categories for different classes of systems and would not need to change with technology. However, there are two serious problems with this approach that eliminate it from consideration. Figure 3.1 illustrates these two problems. This figure shows the benchmark score in sorted records per Joule for varying input sizes (*N*) evaluated on the winning JouleSort system, which is described in detail in Chapter 4. Two different configurations were used to generate this data: for data sets of  $1.5 \times 10^7$  records or fewer, the input and output data were striped across 10 disks using Linux LVM2. For larger data sets, the input and output data were striped across an LVM2 array of six disks, and seven independent disks were used to store temporary data.

As the figure shows, the benchmark score varies considerably with N. The initial steep climb in energy efficiency at the leftmost data points occurs because the smallest data sets take only a few seconds to sort and thus poorly amortize the startup overhead of the sorting program. As the data sets grow larger, this overhead is better amortized and energy efficiency increases, up to a data set of 15 million records. This is the largest data set that can be sorted completely in this machine's memory. For larger data sets, the system cannot perform the entire sort in memory and must temporarily write data to disk, necessitating a second pass over the data that doubles the amount of I/O and dramatically decreases the performance per record. After this transition, energy efficiency stays relatively constant as N grows, eventually trending slowly downward.

The first problem illustrated by this graph is the disincentive to continue sorting beyond the largest one-pass sort. A metric based on a fixed time budget provides no way to enforce continuous progress. To maximize benchmark scores, systems will continue sorting only if the marginal energy cost of sorting an additional record is lower than the cost of sleeping for the remaining time. The incentive to continue diminishes or disappears at the point where an additional record changes the sort from 1-pass to 2-pass. In the 1-pass region of Figure 3.1, the sort is I/O limited, so it does not run twice as fast as a 2-pass sort. It goes fast enough, however, to provide about 40% better energy efficiency than a 2-pass sort. If the system were designed to have a sufficiently low sleep-state power (for this system, 7 W or less), then with a time budget of one minute, the best approach would be to sort 1.5

Figure 3.1: The measured energy efficiency of the current JouleSort-winning system at varying input sizes.

$\times 10^7$  records, which takes 10 seconds, and sleep for the remaining 50 seconds, resulting in a score of 11,800 sorted records per Joule. Thus, for some systems, a fixed time budget defaults into assessing the energy efficiency of a sleeping system, violating the benchmark design goal of balancing power and performance.

The second problem illustrated by this graph is the (*N lg N*) algorithmic complexity of sort, which causes the downward trend for larger *N*. Even in the 2-pass region, total energy is a complex function of many performance factors that vary with *N*: the amount of I/O, the number of memory accesses, the number of comparison operations, CPU utilization, and the amount of parallelism. Figure 3.1 shows that once the sort becomes CPU-bound  $(N \ge 8 \times 10^7 \text{ records})$ , the sorted records per Joule score trends slowly downward because total energy increases superlinearly with *N*. The score for the largest sort on this machine is 9% lower than the peak 2-pass score. This decrease occurs in part because the number of comparisons done in sorting is  $O(N \lg N)$ , and the constants and lower-order overheads hidden by the O-notation are no longer obscured when *N* is sufficiently large. This effect implies that the metric is biased toward systems that sort fewer records in the allotted time. That is, if two fully utilized systems A and B have the same energy efficiency for a fixed number of records, and A can sort twice as many records as B in a minute, the metric of sorted records per Joule will unfairly favor B.

#### **3.2.3** Fixed Input Size

In light of the problems with metrics based on a fixed energy budget or a fixed time budget, a metric based on fixed input size was chosen for the benchmark, as in the Terabyte Sort benchmark. This decision necessitates multiple benchmark classes, similar to the TPC-H benchmark's scale factors [73], since different workload sizes are appropriate for different classes of systems. Three JouleSort classes were chosen, with data set sizes of 100 million records (about 10 GB), 1 billion records (about 100 GB), and 10 billion records (about 1

TB). For consistency, *MB*, *GB*, and *TB* will henceforth be used to denote  $10^6$ ,  $10^9$ , and  $10^{12}$  bytes, respectively.

JouleSort's metric of comparison then becomes the energy to sort a fixed number of records, which is equivalent to the number of records sorted per Joule when the number of records is held constant. The latter metric is preferred for two reasons: first, it makes the power/performance balance more clear, and second, it allows rough comparisons across different benchmark classes, with the caveats described in Section 3.2.2.

This approach has advantages and disadvantages, but it offers the best balance of the design criteria described in Section 2.2. The benchmark classes cover a large spectrum of systems and naturally divide the systems into common classes: laptops, desktops, and servers.

One disadvantage of the fixed time budget is that as technologies improve, benchmark classes may need to be added at the higher end and deprecated at the lower end. For example, if the performance of JouleSort winners improves at the rate of Moore's Law  $(1.6 \times /\text{year})$ , a class of systems which today sorts 10 GB in 100 seconds would take only 10 seconds 5 years from today. Once all relevant systems require only a few seconds for a benchmark class, that class becomes obsolete. Since comparisons across benchmark classes are not perfectly fair, this approach is not fully *history-proof*. However, since even the best-performing sorts are improving more slowly than the Moore's Law rate, these benchmark classes should be reasonable for at least 5 years.

# 3.3 Benchmark Categories

JouleSort, like the other sort benchmarks, has two separate categories within each benchmark class: Daytona, for commercially supported general-purpose sorts, and Indy, for "noholds-barred" benchmark-specific implementations. For Daytona sorts, the hardware components must be unmodified and commercially available, and they must run a commercially supported OS. As with the other sort benchmarks, entrants must report the purchase cost of the system.

# **3.4 Measuring Energy**

While many of the benchmark rules can be borrowed from the existing sort benchmarks, energy measurement requires additional guidelines. The most important areas to consider are the boundaries of the system to be measured, constraints on the ambient environment, and acceptable methods of measuring power consumption.

#### **3.4.1** System Boundaries

The energy measurements should capture all energy consumed by the physical system executing the sort. All power must be measured from the wall and include any conversion losses from power supplies for both AC and DC systems. System power supply inefficiencies can be significant [7], so this policy encourages careful choice of this component. Some DC systems, especially mobile devices, can run from batteries, and those batteries must eventually be recharged, which also incurs conversion loss. While the loss from recharging may be different from the loss from the adapter that powers a device directly, for simplicity, the benchmark permits measurements that include only adapters.

All hardware components used to sort the input records from start to finish, idle or otherwise, must be included in the energy measurement. If some component is unused but cannot be powered down or physically removed from the system, then its power consumption is included in the measurement. If any potential energy is stored within the system, *e.g.* in batteries, the net change in potential energy must be no greater than zero Joules with 95% confidence, or it must be included in the energy measurement. This rule also applies to systems with shared power supplies, such as blades within an enclosure. If the system executing the sort cannot be powered separately from the rest of the enclosure, the total wall power of the enclosure must be reported.

#### **3.4.2** Ambient Environment

The energy costs of cooling can be significant [50], and cooling systems are varied and operate at many levels. A typical data center uses air conditioners, blowers, and recirculators to direct and move air among aisles; and heat sinks and fans to distribute and extract heat away from system components. Given recent trends in energy density, future systems may incorporate liquid cooling [51]. It is difficult to incorporate, anticipate, and enforce rules for all such costs in a system-level benchmark. While air conditioners, blowers, and other cooling devices consume significant amounts of energy in data centers, it would be unreasonable to include their power consumption for all but the largest sorting systems. Therefore, the only cooling costs included in the JouleSort metric are measurable and associated directly with the system being benchmarked. In order to make fair comparisons between systems, the benchmark requires that an ambient temperature between  $20^{\circ}$  and  $25^{\circ}$  C be maintained at the system's inlets, or within one foot of the system if no inlet exists. Energy used by devices physically attached to the sorting hardware that remove heat to maintain this temperature, *e.g.* fans, must be included in the energy measurement.

## **3.4.3** Measurement and Instrumentation

Total energy is the product of the average power over the sort's execution and the wall-clock time to complete the sort. As with the other sort benchmarks, wall-clock time is measured using an external software timer. The easiest method to measure power for most systems will be to insert a digital power meter between the system and the wall. The power meter is subject to the "minimum power-meter requirements" from the SPECpower\_ssj specification [68]. In particular, the meter must report real power instead of apparent power, since

real power reflects the true energy consumed and charged for by utilities [39]. While poor power factors are not penalized, a power factor measured at any time during the sort run should be reported. Finally, since power and time can both vary, a minimum of three consecutive energy readings must be reported. These readings will be averaged, and the system with mean energy lower than all others in its class and category (including previous years) with 95% confidence will be declared the benchmark winner for its class and category.

# 3.5 Summary

The JouleSort benchmark can be summarized as follows:

- Sort a fixed number of randomly permuted 100-byte records with 10-byte keys.

- The sort must start with input in a file on non-volatile store and finish with output in a file on non-volatile store.

- There are three benchmark classes, for workloads of 10<sup>8</sup> (10 GB), 10<sup>9</sup> (100 GB), and 10<sup>10</sup> (1 TB) records.

- Within each benchmark class, there are two categories. The Daytona category is for commercially supported hardware and software, and the Indy category is for "no-holds-barred" implementations.

- The winner in each category is the system with the maximum records sorted per Joule, which is equivalent to minimum energy.

- The energy reported must be total true energy consumed by the entire physical system executing the sort, as measured by a power meter conforming to the SPECpower\_ssj [68] guidelines.

- During the sort, ambient temperature must be maintained between  $20-25^{\circ}$  C.

JouleSort is an I/O-centric, system-level energy-efficiency benchmark that incorporates performance, power, and some cooling costs. It is balanced, portable, representative, inclusive, and simple. It can be used to compare different existing systems, to evaluate the energy-efficiency balance of components within a given system, and to evaluate different algorithms that use these components. These features make it possible to chart past trends in energy efficiency and can help to predict future trends.

Chapter 4

# Designing Energy-Efficient Computer Systems

This chapter assesses the JouleSort energy-efficiency scores of a variety of systems, including the historical sort benchmark winners as well as typical commodity systems. The lessons learned in this evaluation are used to design the CoolSort machine, a fileserver built from low-power mobile components, which is over 3.5 times more energy-efficient than any previous sort benchmark winners. Finally, the JouleSort benchmark's metric is compared to metrics weighing different combinations of performance, price, and power. This analysis shows that systems designed around the JouleSort metric also perform well when cost and performance are weighted more heavily than in the JouleSort metric.

# 4.1 Energy Efficiency of Past Sort Benchmark Winners

This section examines the question of whether any of the existing sort benchmarks can serve as a surrogate for an energy-efficiency benchmark. To do so, we first estimate the sorted records per Joule of the past decade's sort benchmark winners. This analysis reveals that the energy efficiency of systems designed for pure performance (*i.e.* the MinuteSort, Terabyte Sort, and Datamation winners) has improved slowly. On the other hand, systems designed for price-performance (*i.e.* the PennySort winners) are comparatively more energy-efficient, and their energy efficiency is growing more rapidly. However, since Cool-Sort's energy efficiency is well beyond what growth rates would predict for the 2007 PennySort winner, we conclude that existing sort benchmarks do not inherently provide an incentive to optimize for energy efficiency, supporting the need for a JouleSort benchmark.

### 4.1.1 Methodology

Since the winners of previous sort benchmarks were not required to report energy usage, their power consumption while sorting must be estimated. The number of records sorted, the execution time of the sort, and the hardware configuration information were obtained from the previous winners' posted reports at the Sort Benchmark website [62].

The power estimation methodology relies on the fact that the historical sort benchmark winners have used desktop- and server-class components that should have run at or near peak utilization for the duration of the sort. Therefore, component power consumption can be approximated as constant over the sort's length.

Since CPU, memory, and disks are usually the main power-consuming components in a system, individual estimates of these components were used to compute the system power. For GPUTeraSort [21], which made heavy use of a graphics processor, the GPU power was also included in the component estimates.

To estimate the power consumption of memory and disks, per-disk and per-DIMM values from the Hewlett-Packard Enterprise Configurator [28] were used, yielding a fixed power of 13 W per disk and 4 W per DIMM. All of the sort benchmark winners' reports include the number of disks in the system. However, some of the sort benchmark winners' reports only mention total memory capacity and not the number of DIMMs; in those cases, a DIMM size appropriate for the era of the report is assumed. For CPUs, the power estimates are based on the thermal design power (TDP) of the individual CPU(s) used. TDPs are conservative estimates that exceed even the peak power seen in common use; therefore, these numbers were scaled by 0.7 to provide more realistic estimates. When the benchmark reports listed only a CPU family and not the specific model, we assumed the latest possible processor generation given the date of the sort benchmark report, because a given CPU's power consumption decreases as feature sizes shrink. Finally, to account for power supply inefficiencies and for other system components, the total component-level estimates were scaled by 1.2 for single-node systems and 1.6 for clusters; the larger scaling factor for clusters attempts to account for additional networking components.

These coarse-grained power estimates are intended to illuminate broad historical trends and are accurate enough to support the high-level conclusions in this section. The estimation methodology was experimentally validated against the server and desktop-class systems described in Section 4.2.1, for which its accuracy was between 2% and 25%.

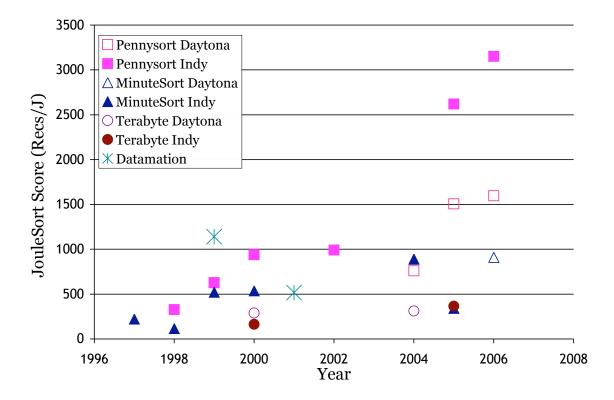

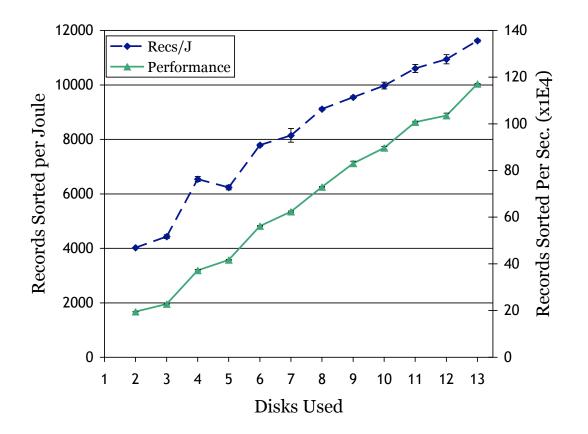

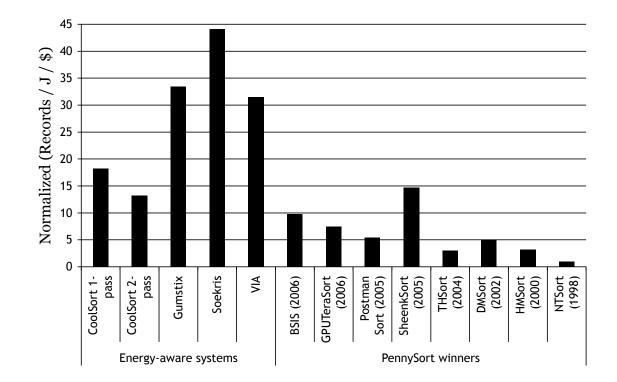

Figure 4.1: Estimated energy efficiency of previous winners of sort benchmarks.

# 4.1.2 Analysis

Although previous sort benchmark winners were not configured with power consumption in mind, they roughly reflect the power characteristics of desktop and higher-end systems in their day. Figure 4.1, which compares the energy efficiency in sorted records per Joule of previous sort benchmark winners, supports a few qualitative observations about the relative improvements in performance, price-performance, and energy efficiency over the last decade.

First, the PennySort winners, which were optimized for price-performance, are clearly more energy-efficient than the winners of the MinuteSort and Terabyte Sort benchmarks, which were optimized for pure performance. There are two reasons for this effect. First, the price-performance metric provides an incentive for system designers to use fewer components, and thus less power. Second, it rewards the use of cheaper commodity components, which, for a given performance point, traditionally have used less energy than expensive, high-performance components.